- Rise Technologies

-

Rise Technology wurde 1993 als privatgeführtes Unternehmen gegründet. Ziel war die Produktion eines konkurrenzfähigen x86-Prozessors mit besonderen Stromsparmechanismen, besonders für Notebooks.

Dies wurde 1998 mit dem Rise mP6 erreicht: Die CPU besaß ein TriplePipelined-Design und konnte u.a. 3 MMX-Instruktionen/Clock ausführen. Die FPU war außerdem auch ein pipelined-Design, was eine hohe Leistung zur Folge hatte. Besonders im Vergleich zur WinChip-Serie von Centaur Technology und der 6x86MX/MII-Serie von Cyrix konnte der Rise mP6 durch eine sehr gute Performance überzeugen.

Die Markteinführung und Verfügbarkeit des Rise mP6 wurde immer wieder verschoben, so dass er nie wirklich auf den Markt kam. Die Nachfolger Rise mP6-II mit integriertem L2-Cache (ähnlich AMDs K6-III) und Tiger S370 wurden nie vorgestellt.

Rise hat dann mit dem iDragon seinen Fokus von Desktop-CPUs auf SoC-Chips gerichtet.

Am 12. Oktober 1999 gab SiS bekannt, dass man die CPU-Technik und anderes Geistiges Eigentum von Rise lizenziert hat. SiS hat die CPU-Technik dann in die SiS55x SoC-Familie integriert. Der CPU-Teil dieses SoC entspricht weitestgehend dem Rise mP6.

Auch STMicroelectronics nutzt Technologie von Rise in seiner CP250-Familie (Vega). Auch diese entspricht weitestgehend dem Rise mP6.

Die Technik des mP6-II oder gar des Tiger S370 ist bis jetzt in keinem anderen Produkt wieder aufgetaucht.

Inhaltsverzeichnis

Modelldaten

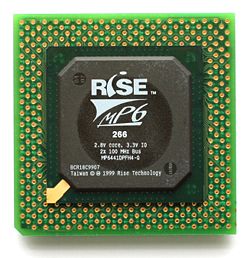

mP6

- Codename:

- 6401 (0.25 µm, Multiplikator 2.0)

- Kirin oder 6441 (0.25 µm, Multiplikator 2.0 und 2.5)

- Lynx oder 6510 (0.18 µm)

- L1-Cache: 8 + 8 KB (Daten + Instruktionen)

- MMX

- Super Sockel 7 (100 MHz FSB)

- DualVoltage

- Betriebsspannung (Vcore): 2,0V (0,18 µm) und 2,8V (0,25 µm)

- Betriebsspannung (I/O): 3,3V

- Besonderheiten:

- schnelle pipelined FPU

- TriplePiplined-Design

- Erscheinungsdatum: Oktober 1998

- Fertigungstechnik: 0,25 µm (später 0,18 µm) bei TSMC

- Die-Größe: 107 mm² (0,25 µm) bei 3,6 Millionen Transistoren

- FSB: 60, 66, 75, 83, 95 und 100 MHz

- Taktraten: 166 MHz bis 250 MHz

- PR166: 166 MHz (83,3 MHz FSB)

- PR233: 190 MHz (95 MHz FSB)

- PR266: 200 MHz (100 MHz FSB)

- PR333: 237,5 MHz (95 MHz FSB)

- PR366: 250 MHz (100 MHz FSB)

mP6-II

- Codename:

- L1-Cache: 8 + 8 KB (Daten + Instruktionen)

- L2-Cache: 256 KB mit Fullspeed

- MMX

- Super Sockel 7 (100 MHz FSB)

- DualVoltage

- Besonderheiten:

- schnelle pipelined FPU

- TriplePiplined-Design

- Erscheinungsdatum: nie erschienen

- Fertigungstechnik: 0,25 µm, später 0,18 µm

- Die-Größe: 105 mm² bei 18 Millionen Transistoren

- Taktraten: 250 MHz bis 350 MHz

- 366: 250 MHz

- 380: 285 MHz

- 400: 300 MHz

- 466: 350 MHz

Tiger S370

- Codename:

- L1-Cache: 8 + 8 KB (Daten + Instruktionen)

- L2-Cache: 256 KB mit Prozessortakt

- MMX

- Sockel 370

- DualVoltage (1,8V Core / 2,5V I/O)

- Besonderheiten:

- schnelle pipelined FPU

- TriplePiplined-Design

- Erscheinungsdatum: nie erschienen

- Fertigungstechnik: -

- Produzent: -

- Taktraten:

Siehe auch

- Codename:

Wikimedia Foundation.