- Single Event Latchup

-

Der Fachbegriff Latch-Up (englisch Single Event Latch-Up; abgekürzt SEL) bezeichnet in der Elektronik den Übergang eines Halbleiterbauelements, wie beispielsweise in einer CMOS-Stufe, in einen niederohmigen Zustand, der zu einem elektrischen Kurzschluss führen kann. Wenn Schutzmaßnahmen fehlen, führt der Latch-Up zur thermischen Zerstörung des Bauteils.

Ausgelöst werden kann ein Latch-Up durch eine kurze elektrische Spannungsspitze, beispielsweise durch Überspannung oder eine elektrostatische Entladung. Daneben kann auch Alpha- oder Neutronenstrahlung einen Latch-Up auslösen. Wegen der (deutlich höheren) Teilchenstrahlung im Weltraum ist daher der Raumfahrteinsatz einiger stark miniaturisierter Bauteile nicht möglich.

Inhaltsverzeichnis

Ursache des Latch-Up-Effektes

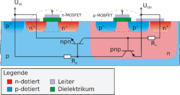

Durch den Schichtaufbau der einzelnen Dotierungen von n- und p-Kanal-Feldeffekttransistoren in einem gemeinsamen Substrat in einer integrierten Schaltung ergeben sich ungewollte parasitäre npn- und pnp-Bipolartransistoren. Diese entsprechen in ihrer gegenseitigen Verschaltung einem Thyristor, wie in nebenstehender Grafik am Beispiel eines Inverters in CMOS-Technik dargestellt ist. Der Latch-Up-Effekt bezeichnet das Zünden (Durchschalten) dieses parasitären Thyristors. Dadurch wird die Versorgungsspannung im Bauteil kurzgeschlossen. Der fließende Strom ist dann hoch genug, um eine thermische Überlastung in diesem Gebiet zu erzeugen und die Schaltung zu beschädigen oder zu zerstören.

Technische Beschreibung

Die kritische geometrische Struktur besteht aus einem parasitären lateralen npn- und einem vertikalen pnp-Transistor. Die Source-Drain-Gebiete des p-Kanal-Transistors sind der Emitter und die n-Wanne die Basis des so entstandenen pnp-Transistors, während das p-leitende Substrat den Kollektor darstellt. Emitter, Basis und Kollektor des npn-Bipolartransistors bilden entsprechend die Source-Drain-Gebiete der n-Kanal-Feldeffekttransistoren, das p-Substrat und die n-Wanne.

Beide Bipolartransistoren sind unter normalen Betriebsbedingungen gesperrt. Fließen aber aufgrund äußerer Bedingungen hohe laterale Ströme durch Wanne und Substrat (beispielsweise durch Überspannung an einem der Eingänge einer CMOS-Schaltung die über, nicht dargestellte, Schutzdioden in das Substrat abgeleitet werden), kommt es an diesen Stellen zu Spannungsabfällen. Diese Spannungen polen die Basis-Emitter-Diode einer der beiden parasitären Transistoren in Flussrichtung. Es kommt zu einem Stromfluss. Der daraus resultierende Kollektorstrom erzeugt einen Spannungsabfall im Basisparallelwiderstand (Rp bzw. Rn) des entstandenen komplementären Transistors. Wird auch bei diesem die Basis-Emitter-Spannung überschritten, leiten nun beide Transistoren. Die Folgen sind eine positive Rückkopplung zwischen den beiden parasitären Bipolartransistoren sowie eine dauerhafte niederohmige Verbindung zwischen der Versorgungsspannung und der Masse. Diese niederohmige Verbindung kann dann nur durch Entfernung der Versorgungsspannung getrennt werden.

Ist die Stromverstärkung eines der beiden Transistoren hoch genug, dann bleibt die Anordnung auch nach dem Verschwinden der injizierten Ströme im aktiven Zustand (Halte- oder Latch-Up-Zustand). Dies führt zu Fehlfunktion des Bauteils, da die Ausgänge auf einem festen Pegel liegen und nicht mehr auf Änderungen des Eingangs reagieren. Der fließende Strom wird außerdem nur durch die Bahnwiderstände und die Widerstände der Basis-Kollektor-Strecken der beteiligten Transistoren bestimmt. Die zuführenden Metallbahnen sind dafür in der Regel nicht ausgelegt, und es kann zu einer thermischen Zerstörung oder Verschmelzung mit darunter liegenden Strukturen kommen.

Auslösemechanismen

- Die Versorgungsspannung überschreitet die absoluten Grenzdaten (engl. absolute maximum ratings) des Bausteins. Eine kurze Spannungsspitze wie bei einer elektrostatischen Entladung kann hier genügen.

- Die Spannung am Eingangs- bzw. Ausgangsanschluss überschreitet die Versorgungsspannung um mehr als den Spannungsabfall einer Diode. Dies kann durch Spannungsspitzen auf einer Signalleitung passieren, z. B. durch Übersprechen.

- Falsche bzw. unzureichende Reihenfolge in der verschiedene Versorgungsspannungen in einer Schaltung eingeschaltet werden (engl. power up sequencing). Noch unversorgte Schaltungsteile, an denen aber schon Signale von bereits versorgten Schaltungsteilen anliegen, können so in den Latch-Up-Zustand gehen.

- Eine weitere unter normalen Umständen eher seltene Ursache ist ionisierende Strahlung, wie Alpha- oder Neutronenstrahlung. Der Latch-Up-Effekt führt bei dem Betrieb von ungeschützten CMOS-Schaltungen in der Nähe von (starken) radioaktiven Strahlungsquellen zu Ausfällen der Elektronik. Auch in diesem Fall kann ein Einzelereignis ausreichen.

Gegenmaßnahmen

Strukturelle Gegenmaßnahmen im Halbleiter

Um die oben beschriebenen auslösenden Mechanismen wirksam zu unterdrücken, können folgende Maßnahmen ergriffen werden:

- Große Abstände der Source-Drain-Gebiete zu den Wannenrändern

- Niederohmiges Substrat und p+-Schutzring (engl. guard ring) neben der n+-Wanne

- Niederohmiger n+-Schutzring für den Versorgungsspannungsanschluss

- Isolierung der einzelnen FETs durch SOI-Substrate

Dabei ergeben sich folgenden Probleme. Auf einem hochdotierten Material (geringer elektrischer Widerstand) lassen sich keine niederohmigen Wannenbereiche implantieren. Daher verwendet man epitaktisch beschichtete Wafer, die eine dünne hochohmige (niedrigdotierte) Siliziumschicht auf dem hochdotierten Material tragen. Die Epi-Schicht nimmt Wannen- und Transistorgebiete auf und das darunter liegende gut leitfähige Substrat sorgt dann für einen wirksamen Latch-Up-Schutz. Der einzige Nachteil dieses Verfahrens sind die hohen Kosten aufgrund des zusätzlichen Beschichtungsverfahren.

Weitere Maßnahmen sind eher baulicher Art und betreffen kurze Anbindungen von Leitungen mit hohen Strömen und die in der Aufzählung bereits erwähnten Guard-Ring-Strukturen. Diese Guard-Ringe sind hochdotierte p+-dotierte Strukturen im p-Substrat und n+-dotierte Strukturen in der n-Wanne. Sie sammeln injizierte Ladungsträger auf und entziehen sie dem Lateralstrom. Guard-Ringe sind nur sehr platzaufwendig zu realisieren, werden aber bei kritischen Ein- und Ausgangsschaltungen in der CMOS-Technologie verwendet.

Moderne CMOS-Schaltungen weisen zur Unterdrückung dieses Störeffektes an den Eingängen spezielle geometrische Anordnungen der Dotierungsbereiche der n- und p-FETs auf. In der Raumfahrt werden auch Schutzschaltungen (schnelle Strombegrenzer) eingesetzt. Eine andere durch Weltraumstrahlung hervorgerufenen Störung, der sogenannte SEU (Single Event Upset), führt nicht zur Zerstörung der Schaltung sondern nur zu einer vorübergenden Störung – je nach Schaltung auch bis zum Blockieren, dies kann jedoch durch Aus-/Einschalten behoben werden. Beide Effekte, SEL und SEU, werden auch als Single Event Effects bezeichnet, da sie von einem einzelnen hochenergetischen Teilchen ausgelöst werden können.

Systematische Gegenmaßnahmen

Es können auch Gegenmaßnahmen außerhalb des Halbleiterbausteins getroffen werden. Im Allgemeinen sind dies Maßnahmen, die sicherstellen, dass die absoluten Grenzdaten des Bausteines nicht verletzt werden:

- Sorgfältiges Power-Sequencing.

- Bei zwei Versorgungsspannungen für das Bauteil kann eine Schottky-Diode zwischen den Versorgungen dafür sorgen, dass diese sich nur um den Spannungsabfall der Diode unterscheiden.

- Strombegrenzung der Versorgung (etwa durch einen Reihenwiderstand). Dieses verhindert zwar nicht den Latch-Up, beugt aber der thermischen Zerstörung des Bauteils vor.

Nachteil dieser Maßnahmen ist, dass die zusätzlichen Bauteile höhere Kosten verursachen. Auch der begrenzte Platz auf einer Leiterplatte kann sich limitierend auf den Einsatz dieser Maßnahmen auswirken.

Standards

- JESD 78A (IC Latch-Up Test)

- Herausgegeben von der JEDEC. Dieser Standard definiert eine Methode, um die Latch-Up-Festigkeit eines integrierten Schaltkreises zu testen. Er definiert außerdem Klassen und Stufen, mit der die Latch-Up-Festigkeit eines Bausteins vergleichbar angegeben werden kann.

Weblinks

Wikimedia Foundation.