- 80535

-

MCS-51 ist die Bezeichnung einer 1980 von Intel vorgestellten Familie von 8-Bit-Mikrocontrollern. Die MCS-51-Familie trat die Nachfolge der MCS-48-Familie an. Zu Beginn hatte sie nur drei Mitglieder mit den Bezeichnungen 8051, 8031 und 8751. Beim 8031 befindet sich das Anwendungsprogramm in einem externen Baustein, wohingegen sich beim 8051 und 8751 das Anwendungsprogramm im Baustein selbst befindet – entweder in einem maskenprogrammierten ROM (8051) oder in einem EPROM (8751).

Intel hat den MCS-51-CPU-Kern an viele Halbleiterhersteller lizenziert und damit die Basis für einen herstellerübergreifenden Industriestandard geschaffen. Seit langem werden MCS-51-kompatible Mikrocontroller nicht nur von Intel, sondern auch von Analog Devices, Atmel, Infineon, Maxim/Dallas, Oki, NXP Semiconductors (Philips), Silicon Laboratories, Texas Instruments u. v. a. hergestellt.

Inhaltsverzeichnis

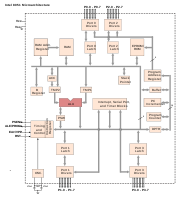

Struktur

Die MCS-51-Familie hat sehr viele Mitglieder hervorgebracht, u. a. den Siemens 80C517. Doch alle haben folgendes gemeinsam:

- 8-Bit Prozessorkern mit einheitlichem Befehlssatz

- mindestens 128 Bytes internes RAM

- externes RAM und ROM

- ein einheitliches Adressierungsmodell für so genannte Special Function Register (SFR)

- Full-Duplex-UART

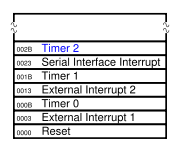

- 5 Interrupt-Quellen

- 2 Interrupt-Prioritäten

- diverse Timer

Aufgrund der unterschiedlichen Befehlslängen von einem bis zu drei Byte sowie den unterschiedlichen Ausführungszeiten für einen Befehl handelt es sich eindeutig um eine CISC-Architektur.

Ein Befehlszyklus entspricht in der ursprünglich von Intel entwickelten Struktur einem bis drei Maschinenzyklen. Ein Maschinenzyklus entspricht 12 Taktzyklen. Heute übliche Varianten des MCS-51 kommen hingegen meist fix mit nur zwei Taktzyklen pro Maschinenzyklus aus. Damit ist bei gleicher Taktfrequenz eine deutlich höhere Befehlsabarbeitung möglich.

Eine Besonderheit dieses Prozessors ist der Bitprozessor, welcher im bitadressierbaren Bereich eine schnelle und einfache Bitmanipulation erlaubt.

Aufgrund der großen Verbreitung dieser Prozessorfamilie und damit verbunden großen Softwarebibliotheken gibt es auch eine Vielzahl von synthetisierbaren MCS-51-Implementierungen. Diese sind als so genannte IP-Cores in einer Hardwarebeschreibungssprache wie beispielsweise VHDL frei und im Quelltext verfügbar [1]. Sie eignen sich für den Einsatz in FPGAs und anwendungsspezifischen integrierten Schaltungen (ASICs). Typische Anwendungsbeispiele sind USB-Controller, wie sie in Druckern oder Schnittstellenadaptern eingesetzt werden. In diese sind zur Steuerung der diversen Protokolle MCS-51-Mikrocontroller integriert.

Bekannteste Varianten

Die MCS-51 umfassen als nicht mehr herstellte NMOS-Varianten ursprünglich unter anderem folgende bekannte Mikrocontroller, alle Speicherangaben sind in Byte:

Typ ROM intern RAM intern Bemerkung 8031 - 128 zwei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen 8032 - 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen 8051 4096 128 zwei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, maskenprogrammierbares ROM 8052 8192 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, maskenprogrammierbares ROM 8751 8192 128 zwei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, EPROM als OTP oder mit UV-Fenster

Die MCS-51 umfassen als CMOS-Varianten ursprünglich unter anderem folgende bekannte Mikrocontroller, alle Speicherangaben sind in Byte:Typ ROM intern RAM intern Bemerkung 80C31 - 128 zwei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen 80C32 - 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen 80C51 4096 128 zwei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, maskenprogrammierbares ROM 80C52 8192 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, maskenprogrammierbares ROM 80C54 16384 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, maskenprogrammierbares ROM 80C58 32768 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, maskenprogrammierbares ROM 87C51 8192 128 zwei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, EPROM als OTP oder mit UV-Fenster. 87C52 8192 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, EPROM als OTP oder mit UV-Fenster. 89C52 32768 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, Flash-Speicher Darüber hinaus gibt es von verschiedenen Firmen erweiterte MCS-51-Mikrocontroller, z.B. von Siemens (heute Infineon) entwickelt und in NMOS-Technologie hergestellt:

Typ ROM intern RAM intern Bemerkung SAB 80515 8192 256 Hersteller: SIEMENS, drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, PWM, 8-fach A/D-Wandler, maskenprogrammierbares ROM SAB 80535 - 256 drei 16-Bit-Timer, 1 UART, zwei externe Interruptquellen, PWM, 8-fach A/D-Wandler Die CMOS-Varianten der Siemens MCS-51-Serie sind funktionsgleich, allerdings nicht in allen Varianten pinkompatibel.

Weitere moderne MCS-51-kompatible Mikrokontroller, welche in CMOS-Technologie mit Flash-Speicher hergestellt werden und meistens schnellere Befehlsverarbeitung, mehr Speicher oder spezielle Schnittstellen aufweisen:

Hersteller Typ Flash intern RAM intern Bemerkung ATMEL AT89C2051 2048 128 nur 20 Pins, kein externer Daten-/Adressbus, zwei 16-Bit-Timer, 1 UART, 1 Komparator, Flash-Speicher ATMEL AT89C4051 4096 128 nur 20 Pins, kein externer Daten-/Adressbus, zwei 16-Bit-Timer, 1 UART, 1 Komparator, Flash-Speicher ATMEL AT89C51ED2 16384 256 bis zu 6 Ports (je nach Gehäusegrösse), 1792 Bytes internes MOVX-SRAM, RS232 Bootloader im ROM, 2048 Bytes internes Daten-EEPROM, drei 16-Bit-Timer, 1 UART, 1 Komparator, 2 Datenzeiger, PWM, SPI, Flash-Speicher MAXIM/DALLAS DS89C430 16384 256 ein Taktzyklus pro Befehl, max. 33 MIPS bei 33 MHz, 1 kB internes MOVX-SRAM, RS232 Bootloader im ROM, drei 16-Bit-Timer, 1 UART, 1 Komparator, 2 Datenzeiger, Flash-Speicher MAXIM/DALLAS DS89C450 65536 256 ein Taktzyklus pro Befehl, max. 33 MIPS bei 33 MHz, 1 kB internes MOVX-SRAM, RS232 Bootloader im ROM, drei 16-Bit-Timer, 1 UART, 1 Komparator, 2 Datenzeiger, Flash-Speicher Speicherorganisation

In der ursprünglichen Form handelt es sich um eine Harvard-Architektur, jedoch besitzen viele neuere MCS-51-Entwicklerboards eine modifizierte Harvard-Architektur. Diese Architektur bedeutet, dass ein Teil des XRAMs (extended data RAM) mittels eines Adressdekoders in den Programmspeicher gespiegelt wird. Dies ermöglicht einer meist ab ROM laufenden Terminalsoftware z.B. per Serielle Schnittstelle kommende Software in den Programmspeicher zu laden und nach dem Übertragen auszuführen.

Der Stack befindet sich immer frei definierbar im internen RAM. Die Byte-Reihenfolge ist Little Endian First.

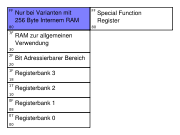

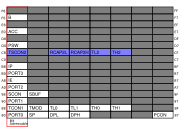

Datenspeicher

Die 4 Registerbänke enthalten jeweils 8 Register, die entweder als Register oder über ihre Adresse ansprechbar sind. Vorteile der Register gegenüber dem "RAM zur allgemeinen Verwendung" sind die kürzeren Befehle. Register 0 und 1 können als 8-Bit-Datenpointer im internen und externen RAM verwendet werden. Durch geschickte Verwendung der Registerbänke lässt sich die Reaktionszeit auf einen Interrupt verkürzen, da die Daten nicht in den Stack verschoben werden müssen.

Da sich das obere RAM und die Special Function Register die Adressen teilen, dient dies zur Unterscheidung die Adressierungsart. Das obere RAM lässt sich nur indirekt mittels Register 0 und Register 1 ansprechen, während die Special Function Register mittels direkter Adressierung ansprechbar sind.

Bei der Programmierung wird das erweiterte RAM (engl. extended data RAM oder kurz XRAM) vom normalen RAM durch den Befehl unterschieden.

MOVspricht das interne RAM an, währendMOVXdas XRAM anspricht. Das XRAM ist nur indirekt adressierbar, dafür jedoch linear. Bei den frühen Varianten war das XRAM immer extern, bei neueren Varianten kann es teilweise oder vollständig integriert sein.Aufgrund der Adressbusbreite von 16 Bit sind bis zu 65536 Byte XRAM möglich.

Die Special Function Register bzw. Speicheradressen des XRAMs werden von bestimmten Varianten von Controllern bzw. Controllerboards für Erweiterungen aller Art verwendet. Als Beispiel:

- weitere Ein- und Ausgänge

- 16 Bit Recheneinheit

- USB-Controller

- ...

Besonders bei den synthetisierbaren MCS-51-Implementierungen bietet sich das an, weil der Befehlssatz der MCS-51 Familie nicht verändert wird, womit die Kompatibilität zu deren Entwicklungstools erhalten bleibt.

Programmspeicher

Da der Adressbus 16 Bit breit ist, kann der externe Programmspeicher bis zu 65536 Byte umfassen. Es kann entweder der interne oder der externe Programmspeicher verwendet werden. Ein gleichzeitiges Betreiben ist nicht möglich.

Mittels

MOVCkann das Programm vom Programmspeicher lesen, was bei der Implementierung von Tabellen hilfreich ist.Ports

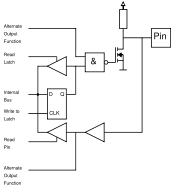

Port 1 und Port 3 dieser Mikrocontroller sind N-Kanal-MOSFETs mit internem Pull-Up.

RMW-Befehle lesen den Wert aus dem Speicher, während alle anderen Befehle die Werte vom Pin holen.

Referenzen

- ↑ Vollständige Implementierung eines MCS-51 Mikrocontrollers in VHDL unter GNU Lesser General Public License (engl.)

Literatur

- Andreas Roth: Das Microcontroller Kochbuch MCS51, mitp Verlag, 6. Aufl., Januar 2002, ISBN 978-3826607226

- J. Koch (Bearb.): Die 8bit-Mikrocontroller-Familie 8051, 1. Eigenschaften. Philips/Valvo, 1984. ISBN 3-87095-260-1

- J. Koch (Bearb.): Die 8bit-Mikrocontroller-Familie 8051, 2. Befehlsvorrat. Philips/Valvo, 1984. ISBN 3-87095-261-X

- Mikrocomputer SAB 8051 Befehlsliste. Hrsg. von der Siemens AG, Bereich Bauelemente, Balanstraße 73, 8000 München 80 (Best-Nr. B/2591)

- Microcontroller Handbook. Intel 1984, Order number 210918-002

- 8-Bit Embedded Controllers. Intel 1991, Order number 270645-003

- R. Leicht: Das große 51er Anwendungsbuch. Franzis Verlag 2005. ISBN 3-7723-5419-X

- J. Walter: Mikrocomputertechnik mit der 8051-Controller-Familie. Springer 1996. ISBN 3-540-60540-1

Weblinks

Wikimedia Foundation.