- 8085

-

Der Intel 8085 ist ein 1976 eingeführter 8-Bit-Mikroprozessor von Intel. Als Nachfolger des Intel 8080 war er zu diesem binär-kompatibel, integrierte jedoch Taktgenerator (8224) und Buscontroller (8228) und besaß eine leistungsfähigere Interrupt-Behandlung. Die 5 im Namen bezog sich auf den Fakt, dass der Prozessor nur eine 5-Volt-Betriebsspannung benötigte. Der 8085 war als CPU für Computersysteme nicht sehr erfolgreich, da er wie sein Vorgänger 8080 vom Zilog Z80 verdrängt wurde. Zum Einsatz kam der Chip in verschiedenen CP/M-Computern sowie als Microcontroller in Büroschreibmaschinen, Oszilloskopen aber auch im Rover der Marssonde Pathfinder. Zählt man jedoch die Mikrocontroller, Embedded Systems und Prozesssteuerungssysteme mit, so ist der 8085 der erfolgreichste Mikroprozessor aller Zeiten, von dem laut Intel im Jahr 2002 mehr produziert wurden als von allen anderen Nachfolgern zusammen.

Inhaltsverzeichnis

Technische Daten

- Taktfrequenz: 5 MHz (andere Versionen mit 2, 3 oder 6 MHz)

- Anzahl: Transistoren 6.500 bei 3 µ

- Datenbus: 8 Bit

- Adressbus: 16 Bit

- in der AH Version 20 % weniger Stromverbrauch gegenüber dem normalen 8085

- Direkt adressierbarer Speicher von 64 KiByte

- 1.3 µs Befehlszyklus (0.8 µs beim 8085AH-2 / 0.67 µs beim 8085AH-1)

- 4 vektorisierte Interrupt-Inputs (einer davon ist nicht maskierbar und ein anderer ist ein 8080A-kompatibler Interrupt)

- Dezimale, binäre und doppelgenaue Arithmetik

- 40-Pin-DIL-Package

Neben dem Intel-Original wird der Prozessor auch von anderen Herstellern, teilweise mit verbesserten Eigenschaften, hergestellt.

Aufbau

Anschlussbelegung und Funktion

Bezeichnung (Symbol)

Pin Eing. (E), Ausg. (A) Funktion A8 – A15, AH 21 – 28 A Adressbus höherwertige 8 Bit der Speicher- oder Portadresse AD0 – AD7,

AL / D0 – D712 – 19 E /A Gemultiplexter Adress- und Datenbus (Zeitmultiplexer) 1. Taktperiode eines Zyklus → Low-Byte einer Adresse 2. und 3. Taktperiode → Datenbus

ALE 30 A Adress Latch Enable, Adressenspeicher Freigabe Signal 1: AD0 – AD7 führen Adresse, ist aktiv beim ersten Taktzyklus während des ersten Maschinenzyklus. Dadurch wird der Adresszwischenspeicher freigegeben.

S0, S1 29, 33 A Maschinenstatussignale, Anzeigen des Betriebszustandes der CPU S1 S0 Betriebszustand 0 0 Warten durch HOLD 0 1 Schreiben 1 0 Lesen 1 1 Funktionscode (Operationcode) holen definiert so zusammen mit IO /M den laufenden Maschinenzyklus

IO/M 34 A Input-Output/Memory, Ein- Ausgabe/Speicher Unterscheidet zwischen Speicher- und Portzugriff 0 → Speicherzugriff 1 → Portzugriff

RD 32 A Read, Lesen (Low-aktiv) 0 → CPU hat den Datenbus freigegeben und erwartet Daten vom Speicher oder Eingabeport 0 ↑ 1 (steigende Flanke) → CPU übernimmt die Daten vom Datenbus

WR 31 A Write, Schreiben (Low-aktiv) 0 → CPU zeigt an, dass gültige Daten auf dem Datenbus liegen

READY 35 E Ready, Bereitschaft 1 → Speicher- oder Portbausteine sind bereit zum Datentransfer 0 → CPU wartet mit Schreib- oder Lesezyklus

HOLD 39 E Hold, Anhalten 1 → eine andere Einheit fordert die Busse an, CPU gibt den Bus frei, sobald die laufende Busoperation beendet ist.

HLDA 38 A Hold Acknowledge, Bestätigung des HOLD-Zustandes HLDA ← 0 wenn HOLD-Aufforderung == 0 Eine halben Taktperiode später übernimmt die CPU den Bus wieder.

INTR 10 E Interrupt Request, Unterbrechungsanforderung allgemeiner Interrupt-Eingang zum Auslösen von Programmunterbrechungen von externen Signalen, wird per Software gesperrt oder freigegeben

INTA 11 A Interrupt Acknowledge, Unterbrechungsannahme wird nach Annahme eines INTR anstelle von RD verwendet → aktivierung eines Interruptbausteines

RSR5.5

RST6.5

RST7.59

8

7E Restart-Interrupts, Neustartunterbrechungen die durch die Befehle SIM und DI maskierbar sind. Alarmmeldung bei 0-1 Übergang. Hier wird nach 3Ch verzweigt. RST7.5 höchste Priorität der RSTs, RST5.5 die niedrigste.

TRAP 6 E Nicht maskierbarer Restart-Interrupt-Eingang RESIN 36 E Reset Input, Rücksetz-Eingang Durch einen Reset wird der Programmzähler auf Null gesetzt. Außerdem werden die HLDA und HOLD Flip‑Flops zurückgesetzt. Während des Resets sind Daten-, Adress- und Meldeleitungen hochohmig geschaltet. Da es sich hierbei um eine asynchrone Leitung handelt, können die internen Register in einen undefinierten Zustand gelangen.

RESOUT 3 A Reset Output, System-Rücksetz-Signal Kann als Systemreset benutzt werden. Dieses Signal ist mit dem Prozessortakt synchronisiert.

X1, X2 1, 2 E Takteingang CLK 37 A Clock, Taktausgang zur Verwendung als Systemtakt. Dieser ist doppelt so hoch als der an X1, X2 eingestellte SID 5 E Serial Input Data, Eingang für serielle Datenübertragung durch Ausführung des RIM-Befehls wird der Wert in den Akkumulator übernommen.

SOD 4 A Serial Output Data, Ausgang für serielle Daten-Übertragung serieller Datenausgang, wird gesetzt oder zurückgesetzt durch einen SIM Befehl.

VCC +5 V 40 Versorgungsspannung (+5 V) VSS GND 20 Masse (0 V) Register

Die 8-Bit-Register können für 16-Bit-Befehle zu Registerpaaren zusammengenommen werden, dies sind A/FLAG, B/C, D/E und H/L. Die Bildung der Registerpaare ist bei den Stackbefehlen PUSH und POP und bei Adressierungs- und Adressrechnungsbefehlen bedeutsam.

Register Reg Funktion / Bedeutung A Akkumulator (8 Bit) B allg. Register (8 Bit) C allg. Register (8 Bit) D allg. Register (8 Bit) E allg. Register (8 Bit) H allg. Register (8 Bit) L allg. Register (8 Bit) FLAG Zustandsregister (8 Bit) INT Interruptregister (8 Bit) IC Befehlszähler (16 Bit) SP Stackpointer (16 Bit) Die allgemeinen Register B, C, D und E dienen im Wesentlichen den logischen und arithmetischen 8-Bit-Operationen, die auch mit den Registern H und L möglich sind, aber vermieden werden sollten. Die letztgenannten Register spielen bei den 16-Bit-Operationen eine gewisse Sonderrolle. Die Ergebnisse der meisten Operationen stehen im Akkumulator A.

Registerpaare

Den Registerpaaren kommen dabei besondere Aufgaben zu, je nach der Art der Adressierung. So können die Registerpaare B/C und D/E benutzt werden, um in indizierter Adressierung Daten vom Arbeitsspeicher zu lesen oder dorthin zu schreiben. Das Paar H/L erlaubt dies nicht, dafür kann es direkt adressiert selbst in den Arbeitsspeicher geschrieben werden, oder von dort gelesen. Ein weiterer Befehl erlaubt den direkten Austausch der Inhalte der Registerpaare D/E und H/L, ebenso den Austausch des Inhalts der aktuellen Stapelspitze (Stackpointer-Position) mit H/L, den Inhalt von H/L in den Stackpointer und auch den Inhalt von H/L in den Befehlszähler zu kopieren. Die Registerpaare können inkrementiert, dekrementiert und zum Registerpaar H/L addiert werden.

Die Technik mit den Registerpaaren wurde im Nachfolgemodell 8086 wesentlich ausgeweitet.

Zustandsregister

Im Zustandsregister sind fünf der acht Bits belegt. Diese haben bei bedingten Sprüngen und Aufrufen die Aufgabe, zu entscheiden, ob eine Sprung- oder Aufrufbedingung erfüllt ist. Dies sind im einzelnen N (negativ) bzw. S (sign), Z (zero – Null), H (half carry – Halbübertrag) bzw. AC (Auxiliary Carry – Hilfsübertrag), P (parity – Parität) und C (Carry – Übertrag).

Zustandsregister 7 6 5 4 3 2 1 0 N/S Z - H/AC - P - C Gesetzt werden die Bits bei allen logischen und arithmetischen 8-Bit-Operationen, nicht jedoch bei Kopier- und Austauschbefehlen. Von den 16-Bit-Befehlen setzt nur die Addition eines Registerpaares zum Paar H/L das Carry-Bit. Wichtig bei Increment- und Decrement-Befehlen ist das Fehlen des C-Bits (Carry), bei 8-Bit-Operationen kann ein Überlauf nur mit dem Z-Bit (Zero) überprüft werden, bei 16-Bitoperationen nur durch nachgeschaltete OR-Befehle.

Interruptregister

Interruptregister (Schreiben und Lesen) 7 6 5 4 3 2 1 0 - 0 - R7.5 MSE M7.5 M6.5 M5.5 - I7.5 I6.5 I5.5 INTE M7.5 M6.5 M5.5 Die Belegung des Interruptregisters ist abhängig von Schreib- oder Lesezugriff und Betriebsart unterschiedlich. Das Register dient im Wesentlichen zur Abfrage und Überprüfung von Interruptzuständen und der Maskierung (Sperrung) einzelner Interrupts. Beim Schreiben (SIM-Befehl) in das Register muss Bit 6 immer 0 sein, um das Register zu verändern, darüber hinaus muss Bit 3 (MSE) auf 1 gesetzt sein, um die Interruptmaskierung in den Bits 0 bis 2 zu übernehmen.

Interrupts und Reset

Hardwareinterrupts Int. Funktion / Bedeutung TRAP (Pin 6) – positiv flankengetriggert RST 5.5 (Pin 9) – positiv pegelgetriggert RST 6.5 (Pin 8) – positiv pegelgetriggert RST 7.5 (Pin 7) – positiv flankengetriggert /RESIN (Pin 36) – negativ pegelgetriggert Interruptvektoren Adresse Auslösung 0000h RESIN / RST 0 0008h RST 1 0010h RST 2 0018h RST 3 0020h RST 4 0024h TRAP 0028h RST 5 002Ch RST 5.5 0030h RST 6 0034h RST 6.5 0038h RST 7 003Ch RST 7.5 kursiv = Softwareinterrupt Gegenüber dem Vorgänger 8080 wurde die Interruptsteuerung deutlich erweitert. Neben dem ursprünglichen Interrupt (durch Interrupt-Controller gesteuert) verfügt der 8085 über vier weitere Interrupteingänge. Die vektorisierten Interrupts und der Reset steuern in 8085 feste Adressen an, ein Konzept, das bei den Nachfolgertypen aufgegeben wurde. Ab dem 8086 werden die Interruptadressen in einer Tabelle in den ersten 1024 Bytes gespeichert.

Adressierung

Der 8085 verfügt über einen Adressraum von nur 64 KBytes für Speicher Zugriffe und 256 Adressen für Portzugriffe. Die Unterscheidung zwischen Speicher- und Portzugriff wird durch einen Ausgang IO/M geregelt, bei Portzugriffen liegt hier ein H an, bei Speicherzugriffen ein L. Als Besonderheit gilt, dass bei Portzugriffen die Portadresse sowohl an AD0 bis AD7 als auch an A8 bis A15 anliegen. Die niederwertigen 8 Bits der Adresse sind gemeinsam mit den Datenbus gemultiplext, das bedeutet, sie teilen sich die gleichen Anschlüsse AD0 bis AD7. Die höherwertigen 8 Bits haben eigene Anschlüsse A8 bis A15. Um anzuzeigen, dass eine gültige Adresse am Bus anliegt, gibt der Prozessor am Ausgang ALE (Address Latch Enable) ein H aus. Die Adresse kann dann in einem externen Speicher zwischengespeichert werden, dabei übernimmt ein negativ flankengetriggerter oder positiv pulsgetriggerter externer Speicherbaustein (meist ein D-Flipflop) den Inhalt von AD0 bis AD7 und gibt dies an die niederwertigen acht Bits des reinen Adressbusses aus. In manchen Schaltungen wird zur Verbesserung des Zeitverhaltens auch das höherwertige Adressbyte A8 bis A15 ebenfalls zwischengespeichert, auch wenn dies für den 8085 eigentlich nicht zwingend erforderlich ist. Über die Ausgänge S0 und S1 wird darüber hinaus der Status des laufenden Maschinenzyklus ausgegeben (siehe Tabelle oben). Durch externe Bausteine kann hiermit eine Adresserweiterung aufgebaut werden, die aber nicht an die Segmentsteuerung der Nachfolgemodelle heranreicht.

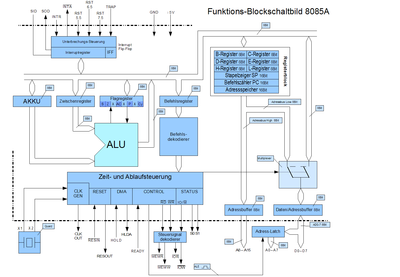

Funktionsblockschaltbild

Maschinenbefehle

Befehlsaufbau

Ein Assembler-Programm besteht aus einer Folge von 8-Bit-Befehlen, in Ausnahmefällen auch Befehlen, die aus 2 aufeinanderfolgenden Bytes bestehen. Die Abarbeitung erfolgt stets sequentiell.Bei einer Wortbreite von 8 Bit sind maximal 256 verschiedene Befehle möglich, von denen beim 8085 aber nur 246 implementiert sind. Bei jedem Befehl enthält das erste Byte den Operationscode (Op-Code), ist also der Operator. Oft ist der Operand, also z. B. der Akkumulator, schon implizit enthalten, dann ist der ganze Befehl nur ein Byte lang. Der Befehl insgesamt kann aber auch 2 oder 3 Byte lang sein:

- 1-Byte-Befehl: Nur Operationscode

- 2-Byte-Befehl: Operationscode + Operand (8-Bit-Konstante oder 8-Bit-Portadresse)

- 3-Byte-Befehl: Operationscode + Operand (16-Bit-Konstante oder 16-Bit-Adresse).

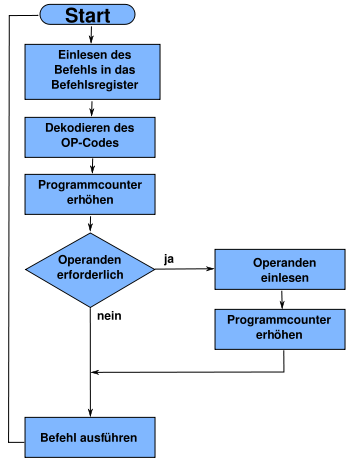

Der Befehlsablauf im Mikroprozessor entspricht dem von-Neumann-Schema. Zunächst wird der Befehl, auf den der Inhalt des Befehlszählregisters (Program Counter, PC, IC) zeigt, geholt und in den Befehlsdekoder gespeichert. Dort wird er dann dekodiert.

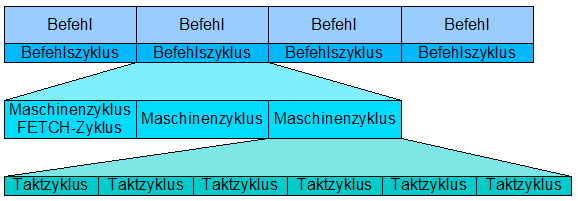

Ein Befehl benötigt 1 bis 5 Maschinenzyklen (Maschine Cycle, Operationszyklen) M1 – M5 Ein Maschinenzyklus besteht aus 3 bis 6 Taktzyklen (States, Operationschritte) T1 – T6

Je nach Befehl wird eine unterschiedliche Anzahl von Maschinenzyklen abgearbeitet. Dies wird im ersten Maschinenzyklus (Befehlsaufruf, FETCH-Zyklus) erkannt.

Befehlszyklen, Maschinenzyklen, Taktzyklen

Die Zeitspanne für einen Maschinenzyklus beträgt etwa 3–6 Takte bei „alten“ Mikroprozessoren. Typische Maschinenzyklen, die innerhalb eines Befehlszyklus auftreten können, sind:

- Befehlsaufruf (OPCODE-Fetch)

- Speicher lesen (Memory Read)

- Speicher schreiben (Memory Write)

- Stapelspeicher lesen (Stack pop)= zweimal Speicher lesen

- Stapelspeicher einschreiben (Stack push) = zweimal Speicher schreiben

- Eingabe (Input)

- Ausgabe (Output)

Befehlsablauf

Befehlssatz

Mnemonic Byte Takte Funktion des Befehls Transferbefehle

Register nach RegisterMOV r1,r2 1 4 r1,r2 = A,B,C,D,E,H,L :Lade Register r1 mit dem Inhalt von Register r2. XCHG 1 4 Vertausche Inhalt der Registerpaare (D,E) und (H,L) XTHL 1 16 Vertausche den Inhalt des Registerpaares (H,L) und den Inhalt des Wortes, das durch den Stackpointer adressiert ist. SPHL 1 6 Lade Stackpointer mit dem Inhalt des Registerpaares (H,L). Speicher, Peripherie nach Register

MOV r1,M 1 7 Lade Register r1 mit dem Inhalt des Speicherbytes das durch den Inhalt des Registerpaares (H,L) adressiert ist. LDA adr 3 13 Akkumulator laden mit dem Inhalt der Adresse adr. LDAX rp 1 7 rp= B,D Akkumulator laden mit dem Inhalt der Speicherzelle die durch den Inhalt des Registerpaares rp adressiert ist. LHLD adr 3 16 Lade Registerpaar (H,L) mit dem Inhalt der Adresse adr und (adr+1) POP rp 1 10 rp= B,D,H,PSW: Registerpaar rp wird mit dem Wort geladen, das durch den Stackpointer adressiert ist IN nr 2 10 Akkumulator wird mit dem Inhalt des Eingabekanal (Nummer nr < 256) geladen Konstante nach Registerpaar

LXI rp, adr 3 10 rp=B,D,H,SPLade Registerpaar rp mit Wert adr. Register nach Speicher, Peripherie

MOV M,r1 1 7 r1 =A;B;C;D;E;H oder L:Inhalt von Register r1 auf den Speicherplatz abspeichern, der durch den Inhalt des Registerpaares (H,L) adressiert ist. STA adr 3 13 Akkumulator-Inhalt unter Adresse adr abspeichern STAX rp 1 7 rp=B,D: Akkumulator in dem Byte abspeichern, das durch den Inhalt des Registerpaares rp adressiert ist. SHLD adr 3 16 Registerpaar(H,L) unter Adresse adr und (adr +1) speichern. PUSH rp 1 12 rp=B,D,H,PSWInhalt des Registerpaares rp wird in das Wort übertragen, das durch den Stackpointer adressiert ist. OUT nr 2 10 Akkumulator wird auf Ausgabekanal (Nummer nr < 256) ausgegeben. Konstante nach Register, Speicher

MVI M,konst 2 10 Lade den Speicherplatz, der durch den Inhalt des Registerpaares (H,L) adressiert ist, mit der Konstanten (konst= Konstante < 256) MVI r1,konst 2 7 r1=A,B,C,D,E,G,H oder L: Lade Register r1 mit der Konstanten (konst < 256) Arithmetische Befehle

INR r1 1 4 r1=A,B,C,D,E,F,H oder L: Zum Inhalt der Registers r1 wird 1 addiert. INR M 1 10 Zum Inhalt des durch Registerpaar (H,L) adressierten Bytes wird 1 addiert. DCR r1 1 4 r1=A,B,C,D,E,F,H oder L: Vom Inhalt des Registers r1 wird 1 subtrahiert. DCR M 1 10 Vom Inhalt des durch Registerpaar (H,L) adressierten Bytes wird 1 subtrahiert. INX rp 1 6 rp=B,D,H,SP: Der Inhalt des Registerpaares wird um 1 erhöht. DCX rp 1 6 rp=B,D,H,SP: Der Inhalt des Registerpaares rp wird um 1 erniedrigt. ADD r1 1 4 r1=A,B,C,D,E,F,H oder L: Inhalt von r1 wird zum Inhalt des Akkumulator addiert. ADD M 1 7 Inhalt des Speicherbytes, das durch den Inhalt des Registerpaares (H,L) adressiert ist wird zum Akkumulator addiert. ADC r1 1 4 r1=A,B,C,D,E,F,H oder L: Inhalt von Register r1 und Inhalt des Carry-Bits werden zum Akkumulator addiert ADC M 1 7 Inhalt des Speicherbytes, das durch den Inhalt des Registerpaares (H,L) adressiert ist und der Inhalt des Carry-Bits werden zum Inhalt des Akkumulators addiert. DAD rp 1 10 rp=B,D,H,SP: Inhalt des Registerpaares rp und der Inhalt des Registerpaares (H,L) werden addiert. Das Ergebnis steht in (H,L). SUB r1 1 4 r1=A,B,C,D,E,H oder L: Inhalt des Registerpaares wird vom Akkumulator subtrahiert. SUB M 1 7 Inhalt des Speicherbytes, das durch den Inhalt des Registerpaares (H,L) adressiert ist, wird vom Akkumulator subtrahiert. SBB r1 1 4 r1=A,B,C,D,E,H oder L: Inhalt von Register r1 und Inhalt des Carry -Bits werden vom Akkumulator-Inhalt subtrahiert. SBB M 1 7 Inhalt des Speicherbytes, das durch das Registerpaar (H,L) adressiert ist und Inhalt des Carry-Bits werden vom Akkumulator subtrahiert ADI konst 2 7 Konstante (konst < 256) wird zum Inhalt des Akkumulators addiert. ACI konst 2 7 Zum Akkumulator-Inhalt werden die Konstante (konst < 256) und das Carry-Bit addiert. SUI konst 2 7 Konstante (konst < 256) wird vom Inhalt des Akkumulators subtrahiert. SBI konst 2 7 Vom Akkumulator-Inhalt werden die Konstante (konst < 256) und das Carry-Bit subtrahiert. DAA 1 7 Akkumulatorinhalt wird in eine zweistellige Zahl umgewandelt. Logische Operationen

CMA 1 4 Akkumulatorinhalt wird negiert. ANA r1 1 4 r1=A,B,C,D,E,H oder L: Akkumulator und der Inhalt des Registers r1 werden UND verknüpft. ANA M 1 7 Der Inhalt des durch Registerpaar (H,L) adressierten Bytes werden mit dem Akkumulator UND verknüpft. ANI konst 2 7 Der Akkumulator wird mit der konstanten (konst < 256) UND verknüpft. ORA r1 1 4 r1=A,B,C,D,E,H oder L:Akkumulatorinhalt wird mit dem Inhalt des Registers r1 ODER verknüpft. ORA M 1 7 Inhalt des über Registerpaar (H,L) adressierten Bytes wird mit dem Inhalt des Akkumulators ODER verknüpft. ORI konst 2 7 Akkumulator-Inhalt wird mit der Konstanten (konst < 256) ODER verknüpft. XRA r1 1 4 Akkumulator wird mit dem Inhalt des Registers r1 EXCLUSIV-ODER verknüpft. XRA M 1 7 Das über Register (H,L) adressierte Byte wird mit dem Akkumulator-Inhalt EXCLUSIV-ODER verknüpft. XRI konst 2 7 Der Akkumulator wird mit der Konstanten (konst < 256) EXCLUSIV-ODER verknüpft. CMP r1 1 4 Akkumulator wird mit dem Inhalt des Registers verglichen. Sind die Werte gleich wird das Zeroflag gesetzt. CMP M 1 7 Akkumulator wird mit dem Inhalt des durch Registerpaar (H,L) adressierten Bytes verglichen. CPI konst 2 7 Akkumulator wird mit der Konstanten (konst < 256) verglichen. Registeranweisungen

Akkumulator rotierenRLC 1 4 Akkumulatorinhalt wird zyklisch um 1 Bit nach links verschoben. Bit 2^7 wird in das Carry-Bit geschrieben. Bit 2^0 = Bit 2^7 RRC 1 4 Akkumulatorinhalt wird zyklisch um 1 Bit nach rechts verschoben. Bit 2^0 wird in das Carry-Bit geschrieben. Bit 2^7 = Bit 2^0 RAL 1 4 Akkumulatorinhalt wird zyklisch um 1 Bit nach links verschoben. Bit 2^7 wird in das Carry-Bit und das Carry-Bit in das Bit 2^0 geschrieben. RAR 1 4 Akkumulatorinhalt wird zyklisch um 1 Bit nach rechts verschoben. Bit 2^0 wird in das Carry-Bit und das Carry-Bit in das Bit 2^7 geschrieben. Übertragsbit-Anweisungen

CMC 1 4 Carry-Bit wird negiert. STC 1 4 Carry-Bit wird gesetzt. Sprungbefehle

Unbedingte Sprünge

PCHL 1 6 Programm wird an der Adresse fortgesetzt die im Registerpaar (H,L) steht. JMP adr 3 10 Programm wird an der Adresse adr fortgesetzt Bedingte Sprünge

JC adr 3 7 / 10 Bei Carry-Bit = 1 wird das Programm bei der Adresse adr fortgesetzt. JNC adr 3 7 / 10 Bei Carry-Bit = 0 wird das Programm bei der Adresse adr fortgesetzt JZ adr 3 7 / 10 Bei Zero-Bit = 1 wird das Programm bei der Adresse adr fortgesetzt JNZ adr 3 7 / 10 Bei Zero-Bit = 0 wird das Programm bei der Adresse adr fortgesetzt JM adr 3 7 / 10 Bei Sign-Bit = 1 wird das Programm bei der Adresse adr fortgesetzt JP adr 3 7 / 10 Bei Sign-Bit = 0 wird das Programm bei der Adresse adr fortgesetzt JPE adr 3 7 / 10 Bei Parity-Bit= 1 wird das Programm bei der Adresse adr fortgesetzt JPO adr 3 7 / 10 Bei Parity-Bit= 0 wird das Programm bei der Adresse adr fortgesetzt Unterprogrammbehandlung

UnterprogrammaufrufeCALL adr 3 18 Programm wird bei der Adresse adr fortgesetzt CC adr 3 9 / 18 Bei Carry-Bit = 1 wird das Programm bei der Adresse adr fortgesetzt CNC adr 3 9 / 18 Bei Carry-Bit = 0 wird das Programm bei der Adresse adr fortgesetzt CZ adr 3 9 / 18 Bei Zero -Bit = 1 wird das Programm bei der Adresse adr fortgesetzt CNZ adr 3 9 / 18 Bei Zero -Bit = 0 wird das Programm bei der Adresse adr fortgesetzt CM adr 3 9 / 18 Bei Sign -Bit = 1 wird das Programm bei der Adresse adr fortgesetzt CP adr 3 9 / 18 Bei Sign -Bit = 0 wird das Programm bei der Adresse adr fortgesetzt CPE adr 3 9 / 18 Bei Parity-Bit= 1 wird das Programm bei der Adresse adr fortgesetzt CPO adr 3 9 / 18 Bei Parity-Bit= 0 wird das Programm bei der Adresse adr fortgesetzt RST konst 1 9 / 18 Programm wird auf der Adresse 8x konst fortgesetzt (konst = 0–7) Rücksprungbefehle

RET 1 10 Programm wird an der Adresse fortgesetzt, die in dem Wort steht, das über den Stackpointer adressiert ist. RC 1 6 / 12 Carry-Bit = 1 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. RNC 1 6 / 12 Carry-Bit = 0 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. RZ 1 6 / 12 Zero -Bit = 1 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. RNZ 1 6 / 12 Zero -Bit = 0 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. RM 1 6 / 12 Sign -Bit = 1 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. RP 1 6 / 12 Sign -Bit = 0 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. RPE 1 6 / 12 Parity-Bit= 1 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. RPO 1 6 / 12 Parity-Bit= 0 wird das Programm an der Adresse fortgesetzt, die in dem über den Stackpointer adressierten Wort steht. Programmunterbrechung

EI 1 4 Interrupt-Flipflop wird gesetzt; Der Mikroprozessor kann eine Unterbrechungsanforderung annehmen DI 1 4 Interrupt-Flipflop wird rückgesetzt. Der Mikroprozessor ignoriert Unterbrechungsanforderungen. Maskenbit Befehle

RIM 1 4 Lies Unterbrechungsmaske und seriellen Eingang in Akkumulator ein. SIM 1 4 Setze Unterbrechungsmaske und seriellen Ausgang. Sonstiger Befehl

HLT 1 5 Programm hält an bis eine Unterbrechungsanforderung eintritt. NOP 1 4 Leerbefehl (No operation) Betriebssystem MAT 85

Einstellung der Schnittstelle: COM 1, 4800, N, 8, 1

Monitor-Kommandos stellen Programmabläufe auf den Bildschirm dar oder ermöglicht den Dialog mit dem Rechner.

Monitor-Kommandos

Kommando Kürzel Funktion BREAKPOINT: B Dieses Kommando erlaubt es, mit dem GO-Kommando Unterbrechungspunkte einzugeben. Unterbrechungspunkte sind Adressen aus dem Speicherbereich des Anwenderprogramms, an denen die Programmbearbeitung unterbrochen werden soll. Nach der Unterbrechung werden die Inhalte der CPU-Register angezeigt. GO: G Mit diesem Kommando können eingegebene Programme gestartet werden. HELP: H Dient dazu, alle verfügbaren Kommandos des Betriebssystems anzuzeigen. IN: I Dieses Kommando dient dazu, Daten von Eingabe-Ports zu lesen und anzuzeigen. MEMORY: M Mit diesem Kommando lassen sich die Inhalte von Speicherzeilen in verschiedenen Formaten (B = Bit, H = Hex, A = ASCII) ausdrucken und ändern. OUT: O Dient dazu, Daten an Ausgabe-Ports zu senden. PRINT: P Mit diesem Kommando können die Inhalte von Speicherzeilen in verschiedenen Formaten (Binär, Hexadezimal, Dezimal, ASCII) formatiert (pro Zeile max. 8 Inhalte) ausgedruckt werden. REGISTER: R Mit diesem Kommando können die Anfangswerte der CPU-Register, z. B. vor einem Testlauf des Anwenderprogramms, vorgegeben werden. Assembler / Disassembler-Kommandos

ASSEMBLER: A Mit diesem Kommando wird ein Programm aufgerufen, das es ermöglicht, Anwendungsprogramme in Mnemo-Code einzugeben. Der eingegebene Code wird Zeile für Zeile in den zugehörigen Maschinen-Code übersetzt und im RAM-Speicher abgelegt. DISASSEMBLER: D Mit diesem Kommando können Programme, die im Maschinen-Code gespeichert sind, in den Assembler-Code übersetzt werden. NEXT INSTRUCTION: N Mit diesem Kommando wird ein Tracer (Verfolger) aktiviert, der es ermöglicht, die Ausführung und Wirkungsweise einer vorgegebenen Anzahl von Programmbefehlen zu verfolgen. dazu wird nach jedem Befehl die Programmbearbeitung kurz unterbrochen und die Inhalte aller CPU-Register werden protokolliert. TRACE INTERVAL: T Dieses Kommando bewirkt eine Protokollierung der Registerinhalte immer dann, wenn diejenigen Programmbefehle abgearbeitet werden, die in einem vorher zu bestimmenden Speicherbereich liegen. Unterprogramme des Betriebssystems

Die in der folgenden Tabelle aufgeführten Unterprogramme aus dem Betriebssystem können in eigenen Programmen verwendet werden. Um die in der Tabelle angegebenen Namen der Unterprogramme in einem Programm mit benutzen zu können, müssen diese Namen mit Hilfe der EQU-Anweisung vorher den zugehörigen Adressen zugewiesen werden.

Unterpr. Name Eingangs Adresse Veränd. Register Funktion KMD0040 Rücksprung in die Kommandoroutine des Assemblers und Ausdruck von KMD>RCHAR0043 A Liest ein Zeichen von der Tastatur ein. der ASCII-Code des Zeichens steht im Akku. Bei [ESC] Rückkehr in die Kommandoroutine und Klingeln. WCHAR0055 Gibt 1 Zeichen, das nach dem CALL-Befehl im speicher steht, auf dem Bildschirm und Drucker (wenn Ein) aus. Das auszugebende Zeichen muss mit derDB-Anweisung in den Speicher geschrieben werden.Beispiel:

CALL 0055 DB 'A' ; A wird ausgegeben

WAHEX0058 Gibt den Akku-Inhalt (8 Bit) als zwei Hexadezimalziffern auf dem Bildschirm und Drucker aus. WHLHEX005B H,L Gibt den HL-Registerinhalt (16 Bit) als vier Hexadezimalziffern auf dem Bildschirm und Drucker aus. WABIN005E A Gibt den Akku-Inhalt (8 Bit) als Binärzahl am Bildschirm und Drucker aus. Beispiel:

MVI A,23 ; 23 Hexadezimal CALL 005E ; wird als 00100011 ausgegeben

WADEZ0061 A Gibt den Akku-Inhalt (8 Bit) als Dezimalzahl auf dem Bildschirm/Drucker aus. Beispiel:

MVI A,23 ; 23 Hexadezimal CALL 0061 ; wird als 35 ausgegeben

WAFOR0064 A,C Gibt den Akku-Inhalt (8 Bit) in einem der zu wählenden Formate ASCII-Binär-Dezimal-Hex auf dem Bildschirm/Drucker aus. Das Format wird durch den Inhalt des Registers C wie folgt gewählt: C Format 0 ASCII-Zeichen 1 Binärzahl 2 Dezimalzahl 3 Hexadezimalzahl Beispiel:

MVI A,23 ; 23 Hexadezimal MVI C,1 ; binär auswählen CALL 0064 ; wird als 00100011 ausgegeben

WBLANK0067 Gibt ein Leerzeichen (space) auf dem Bildschirm/Drucker aus. WBUFI006D Gibt den hinter dem CALL-Befehl stehenden Text auf dem Bildschirm aus. Der Text muss imt derDB-Anweisung in den Speicher geladen werden. Am Ende des Textes muss als Enderkennung eine 0 stehen.Beispiel:

CALL 006D DB 'Dies ist eine Uebung',00

Gibt den Text

Dies ist eine Uebungaus.WCRLFI0073 Gibt einen Wagenrücklauf (CR, carriage return), eine Neue Zeile (LF, line feed) und text in diese neue Zeile aus. Der Text muss wie bei WBUFIvorher eingegeben werden.Beispiel:

CALL 0073 DB 'Text in neuer Zeile',00

HADR08DF Liest eine 16-Bit-Adresse (4 Hex-Stellen) von der Tastatur ein und speichert sie im Doppelregister HL ab. Dabei gelangt der höherwertige Teil der Adresse ins H-Register und der niederwertige Teil ins L-Register. Die Eingabe der Adresse muss mit [ carriage return ] oder [ space ] abgeschlossen werden. BSTIME0895 A,D,E Zeitverzögerung von 0,24 Sekunden. Damit die Inhalte der Register A,D und E vor Aufruf des Unterprogramms gerettet und nachher wiederhergestellt werden, muss die folgende Befehlsreihenfolge eingehalten werden: PUSH PSW ;Programmstatuswort (A, Flags) retten PUSH D ;D retten CALL 0895 ;Zeitverzögerung POP D ;D wiederherstellen POP PSW ;Programmstatuswort (A, Flags) wiederherstellen

CMP20ED8 A Vergleicht die Inhalte der Register DE mit denen der Register HL. Wenn (HL)>(DE) ist, wird das Carry-Flag auf 1 gesetzt, sonst auf 0. Die zu vergleichenden Inhalte müssen vor aufruf des Unterprogramms in die Doppelregister DE und HL geladen werden. Beispiel:

LXI D,Zahl1 LXI H,Zahl2 CALL CMP2

SUB21039 A,HL,DE Subtrahiert die 16-Bit-Zahlen im Doppelregister DE von der 16-Bit-Zahl im Doppelregister HL. Das Ergebnis steht dann im Doppelregister HL. [ (HL) = (HL) - (DE) ]

WBUF0BA1 Bit Text aus einem Textpuffer aus, dessen Anfangsadresse durch den Inhalt des HL-Registers adressiert ist. Der text wird mit der DB-Anweisung ab dieser Adresse geladen, Das Textende muss mit 0 gekennzeichnet sein. Mach der Ausgabe des Textes zeigt das HL-Register auf die adress nach dem Endzeichen.TSTNUM326F A, B, C, D, E, H, L Wandelt eine Dezimalzahl, die in ASCII vorliegt, in eine Binärzahl um. Die ASCII-Zahl muss im speicher stehen, wobei die höherwertigen Stellen die niedrigeren Speicherzellen belegen. Beispiel für die Zahl 123:

Adresse Hex ASCII-Zeichen E000 31 1 E001 32 2 E002 33 3 E004 00 nicht-numerisches Schlusszeichen der erlaubte Wertebereich reicht von 0 bis +65535. Führende Leerzeichen sind erlaubt. Die adresse der ersten Ziffer muss beim Unterprogramm-Aufruf im DE-Register stehen. Die ASCII-Zahl muss mit einem nicht-numerischen Zeichen abgeschlossen sein. Die Binärzahl, die der ASCII-Zahl entspricht, befindet sich nach der Rückkehr im HL-Registerpaar. Die Anzahl der Ziffern steht im B-Register. Fehler: Wird keine Ziffer gefunden, so enthält das B-Register den Wert 00. Wird der zulässige Zahlenbereich überschritten, so enthält das B-Register den Wert FF. Nach dem Rücksprung wird daher folgender Fehler-Test empfohlen:

INR B JZ ueberlauf DCR B JZ keine-Ziffer

TN03272 A, B, C, D, E, H, L Wie TSTNUM, aber keine führenden Leerzeichen erlaubt.DIVIDE3AFE A, B, C, D, E, H, L Dividiert den Inhalt des HL-Registerpaares durch den Inhalt des DE-Registerpaares. Das Ergebnis steht im BC-Register, der Rest im HL-Register. Keine Fehlermeldung bei Division durch Null. PRTNUM3C43 A, B, C, D, E, H, L Druckt eine Zahl in der dezimalsen Schreibweise. Die Zahl muss beim Unterprogramm-Aufruf als Zweierkomplement im HL-Registerpaar stehen (FFFF = −1). Vor positiven Zahlen wird ein Leerzeichen ausgegeben. Nach jeder Zahl wird ein Leerzeichen ausgegeben. Zahlenbereich: −32768 bis +32767. PRTLNN3C46 A, B, C, D, E, H, L Wie PRTNUM. Die Zahl im HL-Registerpaar muss jedoch in normaler Binärcodierung vorliegen (FFFF = 65535). Ist beim aufruf vomPRTLNNdas Sign-Flag im Flag-Register gleich Null, so wird eine positive Zahl ausgegeben. Ist das Sign-Flag gleich Eins, so wird eine negativeZahl (mit vorangestellten „-“) ausgegeben. Beim Aufruf

PRTLNN+1wird das Sign-flag automatisch auf Null (positiv) gesetzt.DRUSWP3ECE Drucker umschalten (Ein/Aus). Beispielprogramm

Einfaches Programm mit Ein- und Ausgabe

; Ein Kommentar wir mit einem Semikolon bzw. Strichpunkt eingeleitet, der Text dahinter wird vom Assembler ignoriert mark: ; eine Marke wird mit einem Doppelpunkt gekennzeichnet star: IN 01 ;Einlesen des Ports 01 OUT 02 ;Ausgabe am Port 02 JMP star ;Ruecksprung zum ProgrammanfangKomplexeres Programm

Dieses Programm stellt ein kleines Lauflicht dar. Es lässt sich mit Bit D7 an der Eingabebaugruppe AN und AUS schalten. Mit Bit D6 wird die Rotationsrichtung festgelegt (rechts oder links) und mit Bit D0 kann man zwischen 2 Laufgeschwindigkeiten wählen. Pause sollte auf 0 und Bit D7 auf 1 gesetzt werden.

;Hauptprogramm MVI B,01 ;Anfangswert fuer Rotation mei: IN 01 ;Ein? (Bit D7=1?) ANI 80 ;Bitmaske fuer D7 JZ mei ;-->MEI, wenn nicht "EIN" MOV A,B ;Lauflicht ansteuern OUT 02 IN 01 ;Linksrotation? (Bit D6=1?) ANI 40 ;Bitmaske fuer D6 JZ rr ;-->RR, wenn keine Linksrotation MOV A,B RLC ;nächste Linksrotation MOV B,A mv: IN 01 ;schnelle Rotation? (Bit D0=1?) ANI 01 ;Bitmaske fuer Bit D0 JZ ze2 ;-->ZE2, wenn langsam CALL ze1 ;sonst Unterprogramm ZE1 aufrufen JMP mei ;Rechtsrotation rr: MOV A,B RRC ;nächste Rechtsrotation MOV B,A JMP mv ;Zeitschleife 1 ze1: LXI D,0001 ;Z laden mz1: DCX D ;Z:=Z-1 MOV A,D ;Z=0? ORA E JNZ mz1 ;-->MZ1, wenn nicht 0 RET ;Rücksprung… ;Zeitschleife 2 ze2: LXI D,0006 ;Z laden mz2: DCR D ;Z:=Z-1 MOV A,D ;Z=0? ORA E JNZ mz2 ;-->MZ2, wenn nicht 0 JMP meiProgramm zum Speicher ausgeben

;Tabellen: ;tab1 ORA 0e100 ;Tabellenadresse DB 01,02,04,08,10,20,40,80,00 ;tab2: ORG 0e200 ;Tabellenadresse DB 01,03,07,0F,1F,3F,7F,0FF,00 ;Hauptprogramm ORA 0e000 ;Startadresse LXI SP,0fc32;Stackpointer mit der Adresse fc32 laden ;eine Null muss bei Hex-Buchstaben vorangestellt werden LC ;Labeltabelle löschen ;Programmfunktion: ;Marken bzw. Labels werden mit einem Doppelpunkt initialisiert star: IN 01 ;Der Hex-Wert vom Eingabe Port mit der ;Adresse 01 wird in den Akkumulator geladen ANI 01 ;UND-Verknüpfung des Hex-Wertes 01 mit dem Akku JZ sch1 ;Wenn das Zero-Flag gesetzt ist, springe zur Marke "sch1" JNZ sch2 ;Wenn das Zero-Flag nicht gesetzt ist, springe zur Marke "sch2" ;1. Unterprogramm sch1: LXI H,0e100 ;Lädt das Registerpaar HL mit der Adresse e100 loo1: MOV A,M ;Der Wert der in der Speicherzelle steht, welche durch das Registerpaar ;HL adressiert ist in den Akku ORA A ;ODER-Verknüpfung des Akkus mit sich selbst JZ star ;Wenn das Zero-Flag gesetzt ist, springe zur Marke "star" OUT 02 ;Der Inhalt des Akkus wird an den Ausgabeport übergeben INX H ;Die Tabellenadresse in HL wird um den Wert 1 erhöht CALL 0895 ;UP-Aufruf ;UP für eine Zeitschleife von 0,2 Sekunden JMP loo1 ;Programmbereich wiederholen, springe nach "loo1" ;2. Unterprogramm sch2: LXI H,0e200 ;Lädt das Registerpaar HL mit der Adresse E200 loo2: MOV A,M ;Der Wert der in der Speicherzelle steht, welche durch das Registerpaar ;HL adressiert ist in den Akku ORA A ;ODER-Verknüpfung des Akkus mit sich selbst JZ star ;Wenn das Zero-Flag gesetzt ist, springe zur Marke "star" OUT 02 ;Der Inhalt des Akkus wird an den Ausgabeport übergeben INX H ;Die Tabellenadresse in HL wird um den Wert 1 erhöht CALL 0895 ;UP-Aufruf ;UP für eine Zeitschleife von 0,2 Sekunden JMP loo2 ;Programmbereich wiederholen, springe nach "loo2" stop: JMP stop ;Endlosschleife, um bei einem Fehler das weiterlaufen des ;Programmes zu verhindern.8085 Software Simulator

Für die Betriebssysteme Microsoft Windows und Linux gibt es unter anderem den kostenlos verfügbaren Open Source Simulator GNUSim8085, der unter der GNU GPL entwickelt und vertrieben wird.

Siehe auch

Weblinks

Mikroprozessoren von Intel | Intel-Prozessoren | ModellnummernNon-x86-Prozessoren: 4004 | 4040 | 8008 | 8080 | 8085 | iAPX 432 | i860 | i960 | Itanium | Itanium 2

Bis 4. Generation: 8086 | 8088 | 80186 | 80188 | 80286 | i386 | i486DX | i486DX2 | DX4 | i486GX | i486SL/SL-NM | i486SX | i486SX2

Pentium-Serie: Desktop: Pentium (MMX) | Pentium II | Pentium III | Pentium 4 | Pentium 4 XE | Pentium D | Pentium XE | Pentium Dual-Core

Mobil: Mobile Pentium 4 | Pentium M | Pentium Dual-Core Server: Pentium Pro

Celeron-Serie: Desktop: Celeron (P6) | Celeron (NetBurst) | Celeron D | Celeron (Core) | Celeron Dual-Core Mobil: Mobile Celeron | Celeron M

Core-Serie: Desktop: Core 2 Duo | Core 2 Quad | Core 2 Extreme Mobil: Core Solo | Core Duo | Core 2 Solo | Core 2 Duo | Core 2 Extreme

Nehalem-Serie: Core i5 | Core i7

Xeon-Serie: Server: Xeon (P6) | Xeon (NetBurst) | Xeon (Core)

Wikimedia Foundation.