- Embedded Wafer Level Ball Grid Array

-

Embedded Wafer Level Ball Grid Array (eWLB) ist eine Gehäusebauform für integrierte Schaltungen, bei der die Gehäuseanschlüsse auf einem aus Chips und Vergussmasse künstlich hergestellten Wafer erzeugt werden.

Inhaltsverzeichnis

Entwicklung

eWLB ist eine Weiterentwicklung der Wafer-Level-Ball-Grid-Array-Technologie (WLB, auch: wafer level package,WLP), die sich dadurch auszeichnet, dass alle notwendigen Bearbeitungsschritte für das Gehäuse auf dem Wafer durchgeführt werden. Dies erlaubt gegenüber den klassischen Gehäusetechnologien (z. B. Ball Grid Array) die Herstellung extrem kleiner und flacher Gehäuse mit exzellenten elektrischen und thermischen Eigenschaften bei besonders niedrigen Herstellungskosten.

Bei WLBs, die auf dem Siliziumwafer hergestellt werden, müssen alle Lötkontakte auf den Chip passen (engl. fan-in design). Daher können lediglich Bausteine mit einer beschränkten Anzahl von Kontakten gehäust werden. Verwandte Bauformen sind Wafer Level Package und Ball Grid Array.

Herstellung

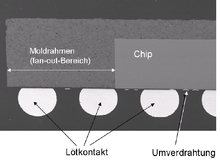

Hingegen erlaubt die eWLB-Technologie Chips mit vielen Kontakten herzustellen. Das Gehäuse wird dabei nicht wie bei klassischen Wafer-Level-Packages auf dem Siliziumwafer sondern auf einem künstlichen Wafer hergestellt. Dazu wird ein im Frontend fertig prozessierter Wafer gesägt und die vereinzelten Chips auf eine Trägerplatte umgesetzt. Die Chips werden dabei in einem größeren Abstand zueinander abgelegt, als dies auf dem Silizium der Fall war. Die Zwischenräume und der Randbereich werden nun durch eine Vergussmasse aufgefüllt. Nach deren Härtung ist ein künstlicher Wafer entstanden, der einen Rahmen aus Vergussmasse (Moldrahmen) um die Chips beinhaltet, auf dem zusätzliche Lötkontakte untergebracht werden können. Nach der Herstellung des künstlichen Wafers, der sogenannten Reconstitution, werden nun wie bei klassischen Wafer-Level-Packages die elektrischen Verbindungen zu den Lötanschlüssen (Verbindungslagen, auch Umverdrahtung genannt) in Dünnschichttechnik hergestellt. Es lassen sich mit dieser Technologie beliebig viele zusätzliche Lötkontakte im gewünschten Abstand auf dem Gehäuse unterbringen (engl. fan-out design). Dadurch lässt sich die Wafer-Level-Packaging-Technologie auch für neue, platzsensitive Anwendungen einsetzen, bei denen die Chipfläche nicht für die Unterbringung der Kontakte in einem realisierbaren Abstand ausreicht. Die eWLB-Technologie wurde von der Firma Infineon entwickelt. Erste Bausteine sind Mitte 2009 auf den Markt gekommen (Mobiltelefon).

Vor- und Nachteile

Als Vorteile kommen die geringen Kosten (Gehäuse und Test), die minimale Gehäuseabmessungen in Höhe und Breite, die exzellente elektrische und thermische Eigenschaft und die unbeschränkte realisierbare Anzahl von Anschlüssen, sowie ein hohes Integrationspotential für Mehrchip- und gestapelte Bausteine und ein aufkommender Gehäusestandard zum Tragen.

Nachteilig wirkt sich die erschwerte Inspektion und Reparatur der Bausteine (visuelle Inspektion nur eingeschränkt möglich) und die mechanischen Spannungen zwischen Gehäuse und Leiterplatte, die stärker zum Bauteil übertragen werden als bei anderen Gehäuseformen aus.

Weblinks

- eWLB. Embedded Wafer-Level Ball Grid Array. STATS ChipPAC, März 2010, abgerufen am 9. August 2010 (PDF, Produktinformation, englisch)

Wikimedia Foundation.