- Chip Scale Package

-

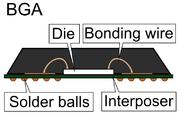

Ball Grid Array (BGA, engl.) bzw. Kugelgitteranordnung ist eine Gehäuseform von Integrierten Schaltungen, bei der die Anschlüsse für SMD-Bestückung kompakt auf der Unterseite des Chips liegen.

Die Anschlüsse sind kleine Lotperlen (engl. balls), die nebeneinander in einem Raster (engl. array, Reihung) aus Spalten und Zeilen stehen. Diese Perlen werden beim Reflow-Löten in einem Lötofen aufgeschmolzen und verbinden sich mit dem Kupfer der Leiterplatte.

Diese Bauform stellt eine Lösung des Problems der Unterbringung einer sehr großen Zahl von Anschlüssen auf einem Bauteil dar. Herkömmliche Dual in-line(DIL)- oder Pin-Grid-Array-Bauformen müssen höhere Mindestabstände zwischen den Anschlüssen haben, um die Kurzschlussbildung während des Lötprozesses zu vermeiden.

Die Chips können trotz der flächigen Verlötung z. B. mit Heißluft wieder von der Leiterplatte entfernt (ausgelötet) werden, ohne Schaden zu nehmen. Die Chips werden ggf. anschließend von den alten Lotperlen befreitet (entlotet, engl. deballing), gereinigt und mit neuen Lotperlen bestückt (Neubeperlung, engl. reballing). Sie können anschließend wieder auf eine neue Leiterplatte gelötet werden. Diese Technik kann auch verwendet werden, um bei der Reparatur von Leiterplatten defekte Chips auszutauschen.

Inhaltsverzeichnis

Vorteile

- geringer Platzbedarf

- Selbstzentrierung beim Löten aufgrund der Oberflächenspannung des Zinns

- gute Wärmeabführung zur Leiterkarte hin

- geringe Impedanz durch kurze Anschlüsse

- Manipulationen an sicherheitsrelevanten Schaltungen sowie Nachahmung erschwert.

Nachteile

- gut eingestellte Reflow-Lötanlage erforderlich

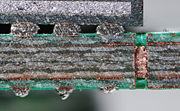

- Inspektion und Reparatur der Lötstellen ist erschwert. Neben Röntgen- und Ultraschallverfahren ist die direkte visuelle Inspektion nur eingeschränkt möglich

- mechanische Spannungen auf der Leiterkarte werden stärker zum Bauteil übertragen als bei bedrahteten Bauteilen oder "gull wing" Pins

- Nur mit spezieller Ausrüstung (geregelter Lötofen) sicher lötbar.

- Inbetriebnahme, Messungen und Reparaturen erschwert, da die Anschlüsse schwerer zugänglich sind.

Verschiedene Typen

Beispiele verschiedener BGA-Typen:

-

- BGA – Raster 0,7–1,5 mm

- FBGA – Fine Pitch BGA, BGA Package mit verringertem Lötpunktabstand (0,5–0,7 mm)

- VFBGA - Very Fine BGA, Raster < 0,5 mm

- FCBGA - Flip Chip BGA

- CBGA – Ceramic Ball Grid Array, wie BGA im Keramikgehäuse

- CSP – Chip Scale Package, kein BGA gehört zu den LLPs (Lead Less Chipcarrier)

Prüfen von BGAs

Zum Prüfen von BGA-Schaltkreisen benötigt man lösbare Adapter, Fassungen oder zum Beispiel Starrnadeladapter (Kontaktieren von Padstrukturen bis herab zu einem Pitch von 150 µm).

Verwandte Bauformen

Weblinks

Wikimedia Foundation.