- Addiernetz

-

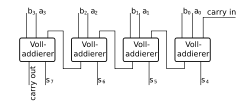

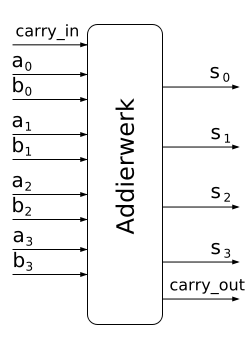

Das Addiernetz bildet aus den Summanden a3..0 und b3..0 die Summe s3..0, carry_in und carry_out ermöglichen die Kaskadierung des Schaltnetzes

Das Addiernetz bildet aus den Summanden a3..0 und b3..0 die Summe s3..0, carry_in und carry_out ermöglichen die Kaskadierung des SchaltnetzesDas Addierwerk ist die Hauptkomponente des Rechenwerks einer CPU.

Das Addierwerk ermöglicht die Addition zweier mehrstelliger Binärzahlen. Da sich alle vier Grundrechenarten auf die Addition zurückführen lassen, bildet es das zentrale Element des Rechenwerks (ALU) eines Prozessors. Während das Addiernetz asynchron funktioniert, arbeitet das Addierwerk getaktet und puffert das Ergebnis mit Speicherbausteinen.

Ein Addierwerk kann auf verschiedene Arten realisiert sein, die bekanntesten Schaltungen sind das Paralleladdierwerk, das Serienaddierwerk und das Von-Neumann-Addierwerk. Alle drei verwenden Voll- und/oder Halbaddierer zur Durchführung der Addition.

Inhaltsverzeichnis

Schaltungstypen

Paralleladdierwerk

In der Grundform wird der Carry-Ripple-Addierer als Addiernetz verwendet, wobei das Carry-Out mit Carry-In des nächsten Volladdieren verbunden wird. Zur Bildung der Summe muss das Signal im Worst-Case das Carry-Bit vom Niederwertigsten Addierer bis zum höchstwertigsten Addierer wandern. Daraus folgt bei großen Rechenwerken eine erhebliche Laufzeiten im Addiernetz, in der Folge wurden Schaltnetze mit reduzierter Laufzeit entwickelt.

- Paralleladdierer mit Übertragsumleitung (Carry-Skip-Addierer), die Volladdierer werden zu Gruppen zusammengefasst und durch Zusatzlogik wird schnell ermittelt, ob ein Carry-In die Gruppe durchwandert (Bei allen Addierern liegt mindestens an einem Eingang eine 1, somit haben alle einzelnen Addierer eine Übertrag im Ergebnis.

- Paralleladdierer mit Übertragsvorausberechnung (Carry-Look-Ahead-Addierer), das Schaltnetz für eine Addierer Gruppe enthält eine aufwendige Logik, die deren Übertrag direkt ermittelt.

- Conditional-Sum-Addierer, berechnet für eine Addierergruppe das Ergebnis, sowohl mit als auch ohne Carry-In gesetzt. Eine Auswahl-Logik schaltet in Abhängigkeit vom Carry-In das entsprechende Ergebnis zu den Ausgängen.

Der Vorteil des Paralleladdierers liegt in der gleichzeitigen Arbeit aller beteiligten Addierer. Der Nachteil der Grundform sind die langen Signal-Laufzeiten, da sich der Übertrag im Extremfall von rechts nach links durch die Schaltung propagieren muss. Die Weiterentwicklungen benötigen eine große Zahl zusätzlicher Gatter, deren Zahl linear mit der Breite n der zu addierenden Stellen des Dualsystems steigt.

Serienaddierwerk

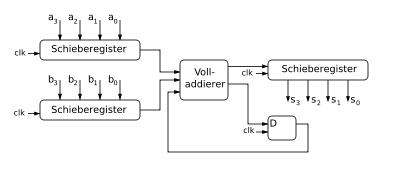

Das Serienaddierwerk benötigt einen Volladdierer sowie einen D-Flip-Flop zur Addition zweier n-stelliger Binärzahlen. In jedem Takt wird das äußerste rechte Bit der Binärzahlen aus den Schieberegistern sowie der Wert im D-Flip-Flop in den Volladdierer übertragen. Das Ergebnis wird in einem Register gespeichert und der Überlauf im D-Flip-Flop für den nächsten Takt gespeichert. Der Vorteil des Serienaddierwerks liegt in der geringen Anzahl der benötigten elektronischen Bauteile. Der Nachteil liegt in der seriellen Abarbeitung, so dass n Takte zur Addition zweier n-stelliger Binärzahlen nötig sind.

Die Kombination der Vorteile des Parallel- und Serienaddierers führt zum Von-Neumann-Addierwerk-

Von-Neumann-Addierwerk

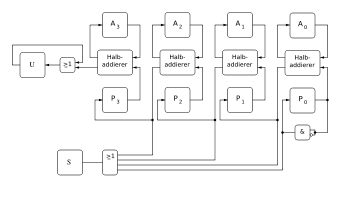

Das Von-Neumann-Addierwerk benötigt n Halbaddierer zur Addition zweier n-stelliger Binärzahlen. Die Addition erfolgt durch folgenden Algorithmus

Wiederhole

- Register A und P mit Summanden Laden

- Addieren

- Register A mit Summen ohne Übertrag laden, in P Überträge laden

- Aktion 2 und 3 solange wiederholen bis Register S Null ist

Das AND an P0 sorgt dafür, das nach dem ersten Addierdurchlauf P0 von da an mit 0 gesetzt wird.

Das Addierwerk benötigt im ungünstigsten Fall („worst-case“) n+1 Takte; die Erfahrung der Praxis zeigt, dass es im Mittel nur log2n + 1 sind.

Beispiel 13 + 11:

Schritt S U P3...0 A3...0 0 0 0000b 0 0000b 1 1 0 1101b 13 1011b 11 2 1 1 0010b 2 0110b 22 3 1 1 0100b 4 0100b 20 4 1 1 1000b 8 0000b 16 5 0 1 0000b 0 1000b 24 Subtrahieren

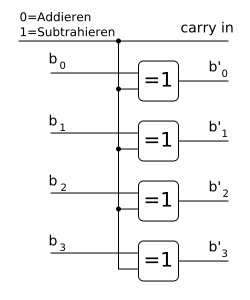

Die Subtraktion ist mit der Addition eng verwandt und lässt sich durch Vorzeichenwechsel des Subtrahenden in eine Addition umwandeln. Ein Vorzeichenwechsel bei Dualzahlen ermöglicht das Zweierkomplement, umgesetzt als Einerkomplement (invertieren aller Bits) und danach mit 1 addiert (setzen von carry in). Die Erweiterung des Addierwerks zum Addier-/Subtrahierwerk ermöglicht die Vorschaltung von XOR-Verknüpfungen am Eingang des zweiten Operanden. Steht der Wahlschalter auf 1 invertiert das XOR das Eingangssignal und setzt das Carry-In-Bit, hierdurch entsteht das Zweierkomplement und aus der Addition wird eine Subtraktion.

Addition und Subtraktion von Gleitkommazahlen

Viele Prozessoren verfügen über eine Gleitkommaeinheit für Berechnungen mit Kommazahlen. Bei Gleitkommazahlen werden Mantisse und Exponent getrennt verarbeitet. Dazu werden die Exponenten der Zahlen in einem Normierer angeglichen, die Zahlen mit Hilfe eines Addierer/Subtrahierer addiert und schließlich wird das Ergebnis und der neue Exponent in einem Normierer zu einer neuen Gleitkommazahl – dem Ergebnis – verarbeitet.

- Normierer

Zuerst muss der Exponent angeglichen werden. Dazu werden die beiden Exponenten subtrahiert und die Mantisse der Gleitkommazahl mit dem kleineren Exponenten mit einem Schieberegister um die durch die Subtraktion der Exponenten ermittelte Anzahl an Stellen (Bits) verschoben. Dadurch besitzen beide Zahlen denselben (größeren) Exponenten. Der größere Exponent wird über einen Multiplexer anhand des Vorzeichens des bei der Subtraktion entstandenen Wertes (Exponenten-Differenz) ausgewählt und direkt an den Normierer weitergeleitet.

- Addierer/Subtrahierer

In der Addierer/Subtrahierer-Stufe arbeitet im Wesentlichen ein Addierer mit vorgeschalteten Invertern an den Eingängen. Die Inverter invertieren (negieren) die Mantisse, wenn das zugehörige Vorzeichen-Bit der jeweiligen Gleitkommazahl gesetzt ist. Anschließend können die beiden Zahlen addiert werden. Hierbei entsteht die neue Mantisse. Zudem wird das Prioritäts-Bit (Überlauf-Bit) des Addierers gesetzt, wenn die Summe der beiden Mantissen zu groß ist um in der neuen Mantisse gespeichert werden zu können.

- Normierer

Im Normierer wird die Exponenten-Differenz um eins reduziert und das Ergebnis aus der Addierer/Subtrahierer-Stufe um eins nach links verschoben, falls das Prioritäts-Bit gesetzt ist. Anschließend wird das Ergebnis aus der Addierer/Subtrahierer-Stufe zur Mantisse – und die Exponenten-Differenz zum Exponenten – der Ergebnis-Gleitkommazahl.

Weblinks

Wikimedia Foundation.