- Harvardarchitektur

-

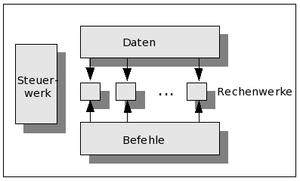

Die Harvard-Architektur bezeichnet in der Informatik ein Schaltungskonzept zur Realisierung besonders schneller CPUs und Signalprozessoren. Der Befehlsspeicher ist physisch vom Datenspeicher getrennt und beide werden über getrennte Busse angesteuert. Der Vorteil dieser Architektur besteht darin, dass Befehle und Daten gleichzeitig geladen, bzw. geschrieben werden können. Bei einer klassischen Von-Neumann-Architektur sind hierzu mindestens zwei aufeinander folgende Buszyklen notwendig.

Zudem sorgt die physikalische Trennung von Daten und Programm dafür, dass bei Softwarefehlern kein Programmcode überschrieben werden kann. Nachteilig ist allerdings, dass nicht benötigter Datenspeicher nicht als Programmspeicher genutzt werden kann.

Die Harvard-Architektur wurde zunächst überwiegend in RISC-Prozessoren konsequent umgesetzt. Moderne Prozessoren in Harvard-Architektur sind in der Lage, parallel mehrere Rechenwerke gleichzeitig mit Daten und Befehlen zu füllen. Bei Signalprozessoren der C6x-Familie von Texas Instruments ist dies beispielsweise für bis zu acht Rechenwerke möglich.

Ein weiterer Vorteil der Trennung ist, dass die Datenwortbreite (die kleinste adressierbare Einheit) und Befehlswortbreite unabhängig festgelegt werden kann. Damit kann auch, wenn erforderlich, die Effizienz des Programmspeicherbedarfs verbessert werden, da sie nicht direkt von den Datenbusbreiten abhängig ist, sondern ausschließlich vom Befehlssatz. Dies kann z.B. in eingebetteten Systemen oder kleinen Microcontroller-Systemen von Interesse sein.

Besonders bekannte Vertreter dieser Architektur sind die Produkte der Firma Microchip Technology Inc. (PICmicro). Ebenso basieren die Mikrocontroller der AVR-Reihe von Atmel auf der Harvard-Architektur.

Eine bedeutende Erweiterung der Harvard-Architektur wurde von der amerikanischen Firma Analog Devices Anfang der 1990er Jahre durch die Einführung der SHARC-(Super-Harvard-Architecture)-Technologie vorgenommen, bei der die genannten Speichersegmente als Dual-Port-RAMs ausgeführt sind, die kreuzweise zwischen den Programm- und Daten-Bussen liegen.

Viele moderne Prozessoren verwenden eine Mischform aus Harvard- und von-Neumann-Architektur, bei der innerhalb des Prozessorchips Daten und Programm voneinander getrennt verwaltet werden, eigene Caches und MMUs haben und über getrennte interne Busse laufen, extern jedoch in einem gemeinsamen Speicher liegen.

Einer der ersten bedeutenden Prozessoren, die die Harvard-Architektur intern einsetzten, war der Motorola 68030.

Siehe auch

Wikimedia Foundation.