- Leiterplattenlayout

-

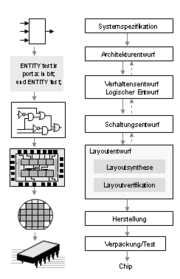

Unter Layoutentwurf einer elektronischen Schaltung (Schaltkreis, Multi-Chip-Modul, Leiterplatte) versteht man das Erstellen und die Verifikation der geometrischen Anordnung der Zellen bzw. Bauelemente und ihrer Verbindungen. Die Verifikation innerhalb des Layoutentwurfs umfasst i.Allg. die Prüfung des entworfenen Layouts auf Einhaltung aller technologischen und elektrischen Regeln.

Inhaltsverzeichnis

Layouterstellung (Layoutsynthese)

Bei der Erstellung des Schaltungslayouts überführt man unter Nutzung von Bibliotheks- und Technologie-Informationen die Netzliste einer Schaltung in ihre reale geometrische Darstellung. Dabei werden alle Schaltungselemente (Zellen/Gatter, Makrozellen, Transistoren usw.) in ihrem geometrischen Abbild (Form, Abmessung, Ebenenzuordnung) dargestellt und ihre räumliche Anordnung (Platzierung) sowie die konkreten Verbindungsstrukturen (Verdrahtung) zwischen ihnen ermittelt. Im Ergebnis liegt die Layoutdarstellung der Schaltung vor, die nach einer Layoutverifikation zur Herstellung des Verdrahtungsträgers (Schaltkreis, Multi-Chip-Modul, Leiterplatte) genutzt wird.

Aufgrund ihrer Komplexität wird die Layouterstellung in einzelne Teilabschnitte unterteilt. Beim digitalen Schaltkreis- bzw. Chipentwurf ist es üblich, die Schritte Partitionierung, Floorplanning, Platzierung, Global- und Feinverdrahtung sowie ggf. Kompaktierung, durchzuführen. Wesentliche Schritte bei Leiterplatten sind die Platzierung der Bauelemente und die Leiterplattenentflechtung.

Die automatisierte Layouterstellung bei integrierten Schaltkreisen wird oft als Layoutsynthese bezeichnet.

Layoutverifikation

Der Layouterstellung schließt sich eine umfassende Verifikation des Layouts auf seine technologische Realisierbarkeit, die elektrische Korrektheit und seine elektrische Funktionstüchtigkeit an.

Beim DRC (Design Rule Check) verifiziert man die Realisierbarkeit des Layouts, indem die Einhaltung der technologisch bedingten Entwurfsregeln in der Layoutdarstellung kontrolliert wird.

Ebenfalls zur Verifikation des Schaltungslayouts dient die Extraktion, bei der Layoutinformationen zur Verifikation aufbereitet werden. So lässt sich beispielsweise aus dem Layout eine Netzliste extrahieren, welche man anschließend beim sog. LVS (Layout Versus Schematic) mit der aus dem Schaltplan abgeleiteten (ursprünglichen) Netzliste auf Gleichheit prüft, um die elektrische Korrektheit des Layouts festzustellen. Bei der Parameter- bzw. Parasitenextraktion werden aus den geometrischen Eigenschaften der Layoutstrukturen deren elektrische Parameter abgeleitet, um sie dann unter Einschluss der Netzliste zur Validierung der elektrischen Eigenschaften des Schaltungslayouts zu benutzen. Beim ERC (Electrical Rule Check) prüft man die elektrische Funktionstüchtigkeit des Layouts, wie z.B. die Einhaltung eines maximalen Widerstandswertes zwischen zwei Netzanschlüssen.

Vom Layout zur integrierten Schaltung

Die Layoutinformationen werden, oft in Form von GDSII-Daten, an die den Schaltkreis fertigende Einrichtung, die sog. Fab oder Foundry, übergeben. Dieser Vorgang wird noch heute als „Tape out“ bezeichnet, obwohl die Datenübertragung nicht mehr wie früher mittels Magnetband stattfindet.

In der Fab erfolgt zuerst die Umsetzung der lagenspezifischen Layoutinformationen in photolithographische Masken. Diese Masken dienen zur Belichtung des auf dem Silizium befindlichen Photolacks in technologisch genau definierten Abbildungsschritten des Layouts. Mittels der photolithographischen Masken lassen sich somit Flächen auf dem Silizium definieren, wo Materialien aufgetragen, verändert oder abgetragen werden sollen.

Eine Vielzahl von integrierten Schaltungen entstehen dabei parallel auf einer Siliziumscheibe, dem Wafer. Die einzelnen noch unverpackten Schaltungen, die sog. Dies oder Nacktchips, werden auf dem Wafer (vor-)getestet und als „gut“ oder „schlecht“ gekennzeichnet. Abschließend wird der Wafer in die einzelnen Dies zersägt. Die als „gut“ gekennzeichneten Dies werden in einem Schaltkreisgehäuse angeschlossen und verpackt.

Vom Layout zur Leiterplatte

Ergebnis des Layoutentwurfs sind für die Leiterplattenherstellung die sog. Gerber-Dateien. Diese beschreiben für jede Lage (engl. Layer) die Koordinaten der Polygone, welche die Leiterzüge definieren, sowie die der Blenden (engl. Apertures) für den Fotoplotter. Zusätzlich werden für die Fertigung noch Dateien benötigt, die die Position und den Durchmesser der Bohrungen und die Koordinaten der Leiterplattenkontour oder von Ausfräsungen beschreiben. Diese sind werkzeugabhängig.

Vor der Fertigung werden meist mehrere Leiterplatten zu einem sog. Los zusammengefasst, um die bei der Produktion zur Verfügung stehende Leiterplattenfläche bestmöglich auszunutzen.

Siehe auch

Literatur

- J. Lienig: Layoutsynthese elektronischer Schaltungen – Grundlegende Algorithmen für die Entwurfsautomatisierung; Springer (2006), Berlin, Heidelberg, New York, ISBN 3-540-29627-1.

- Ch. Saint, J. Saint: IC Mask Design – Essential Layout Techniques; McGraw Hill, New York, 2002, ISBN 0-07-138996-2.

- J. Händschke: Leiterplattendesign – Ein Handbuch nicht nur für Praktiker; Eugen G. Leuze Verlag (2006), Bad Salgau, ISBN 3-87480-219-1.

Weblinks

GMM/GI/ITG-Fachgruppe "Entwurf des Layouts von Schaltungen" (http://www.fachgruppe-layout.de)

Wikimedia Foundation.