- NAND-ROM

-

geöffneter USB-Stick – der linke Chip ist der eigentliche Flashspeicher, der rechte ein Mikrocontroller.

Ein Flash-EEPROM (linkes IC), wie es z. B. für die Speicherung des BIOS von PCs verwendet wird.

Ein Flash-EEPROM (linkes IC), wie es z. B. für die Speicherung des BIOS von PCs verwendet wird.Flash-Speicher sind digitale Speicherchips; die genaue Bezeichnung lautet Flash-EEPROM. Im Gegensatz zu „gewöhnlichem“ EEPROM-Speicher lassen sich bei neuen Flash-EEPROM Bytes, die kleinsten adressierbaren Speichereinheiten, nicht einzeln löschen.

Inhaltsverzeichnis

Geschichte

Bezeichnung und Name

Der Name „Flash“ kam gemäß einer Anekdote aus dem Entwicklungslabor von Toshiba 1984 so zustande: Shoji Ariizumi, einen Mitarbeiter des Projektleiters Dr. Fujio Masuoka, erinnerte der in Blöcken stattfindende Löschvorgang des Speichers an das blendende Licht eines Kamerablitzes. Er schlug deshalb den Namen „Flash“ vor.

Entwicklungsgeschichte

Die Geschichte der Flash-Speicher ist eng verbunden mit der Geschichte der Digitalkamera. Das erste Compact-Flash-Medium mit vier Megabyte Kapazität wurde 1994 von SanDisk vorgestellt. 1998 stellte Sony den ersten Memory Stick vor.

Heute (2009) finden Flash-Speicher überall dort Anwendung, wo Informationen persistent (nichtflüchtig) auf kleinstem Raum – ohne permanente Versorgungsspannung – gespeichert werden müssen. Dazu zählen auch weiterhin Speicherkarten für Digitalkameras und andere mobile Geräten wie Mobiltelefone, Handhelds. Andere Bauformen beziehungsweise Geräte, in denen diese Speichertechnologie genutzt wird, sind USB-Sticks und MP3-Player sowie DiskOnChip. Letztere dienen beispielsweise für die dauerhafte Speicherung der Firmware in vielen Geräten mit Mikrocontrollern (Eingebettete Systeme, BIOS); zum selben Zweck zunehmend auch auf dem Microcontroller selbst integriert: embedded flash.

Zunehmend im Interesse steht der Einsatz als Hauptspeichermedium in Computersystemen. Hier sollen Flash-Speicher in Form sogenannter „Solid State Drives“ (dt. Festkörperlaufwerk) zukünftig die herkömmlichen Festplatten (engl. hard disk drive) ersetzen bzw. unterstützen (vgl. Hybridfestplatten).

Funktionsprinzip

Überblick

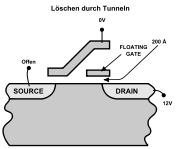

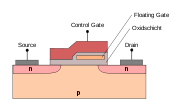

Bei einem Flash-EEPROM werden Bits in Form von elektrischen Ladungen auf einem sogenannten „Floating-Gate“ eines Feldeffekttransistors gespeichert (bei neueren Speichern auch mehrere Bits pro Gate, da verschiedene Ladungszustände benutzt werden), das von der Stromzufuhr durch eine Schicht eines Isolators abgeschnitten ist (daher das „Floating“ im Namen), sodass dort gespeicherte Ladung nicht einfach abfließen kann. Eine Änderung des Ladungszustands kann nur mithilfe des quantenphysikalischen Tunneleffekts geschehen, der es den Elektronen erlaubt, den eigentlichen Nichtleiter zu passieren.

Speichern und Lesen

Die Speicherung eines Bits erfolgt über das Floating-Gate, das eigentliche Speicherelement des Flash-Feldeffekttransistors. Es liegt zwischen dem Steuer-Gate und der Source-Drain-Strecke und ist von dieser wie auch vom Steuer-Gate jeweils mittels einer Oxid-Schicht isoliert. Im ungeladenen Zustand des Floating-Gate kann im über das Steuer-Gate aufgesteuerten Transistor in der Source-Drain-Strecke (Kanal) ein Strom fließen. Werden über das Steuer-Gate durch Anlegen einer hohen positiven (10–18 V) Spannung Elektronen auf das Floating-Gate gebracht, so kann in der Source-Drain-Strecke auch bei aufgesteuertem Transistor kein Strom mehr fließen, da das negative Potential der Elektronen auf dem Floating-Gate der Spannung am Steuer-Gate entgegen wirkt und somit den Flash-Transistor geschlossen hält.

Der ungeladene Zustand wird wieder erreicht, indem die Elektronen durch Anlegen einer hohen negativen Spannung über die Steuergate-Kanal-Strecke wieder aus dem Floating-Gate ausgetrieben werden. Dabei ist es sogar möglich, dass der Flashtransistor in den selbstleitenden Zustand gerät, d. h. er leitet sogar dann Strom, wenn am Steuer-Gate keine Spannung anliegt („Over-Erase“): statt mit Elektronen ist das Floating-Gate nun quasi mit positiven Ladungsträgern (Defektelektronen, 'Löchern') besetzt. Das ist insbesondere in NOR-Architekturen (s. u.) problematisch.

Tunneleffekt

Der Mechanismus, der die Elektronen durch die isolierende Oxidschicht passieren lässt, wird Fowler-Nordheim-Tunneleffekt genannt (nach ihren ersten Erforschern), d. h. bei einem Flashspeicher handelt es sich um die Anwendung eines nur quantenmechanisch deutbaren Effekts. Um die Wahrscheinlichkeit, dass Elektronen zum Floating-Gate tunneln, zu erhöhen, wird oft das Verfahren CHE (engl. channel hot electron) verwendet: Die Elektronen werden durch Anlegen einer Spannung über dem Kanal, also zwischen Drain und Source, beschleunigt und dadurch auf ein höheres Energieniveau (daher engl. hot) gehoben, wodurch sie schon bei geringeren Spannungen (typ. 10 V) zwischen Gate und Kanal zum Floating-Gate tunneln. (In obiger Abbildung zum Programmieren ist dieses Verfahren – allerdings für eine ältere Technik – angedeutet.)

Anmerkung

Ob der geladene oder ungeladene Floating-Gate-Zustand als jeweils '0'- oder '1'-Zustand der Speicherzelle angesehen wird, ist implementierungsabhängig. Per Konvention wird aber meist derjenige Zustand des Floating-Gate, der durch blockweises Löschen hergestellt wird, als '0' ("gelöscht") bezeichnet. Entsprechend bezeichnet man den bitweise einstellbaren Zustand als '1' („programmiert“) [1].

Ansteuerung

Ein Flash-Speicher besteht aus einer bestimmten, von der Speichergröße abhängigen Anzahl einzelner Speicherelemente. Die Bytes oder Worte (typisch durchaus bis 64 Bit) können einzeln adressiert werden. Dabei können sie in einigen Architekturen auch einzeln geschrieben werden, wogegen bei anderen nur größere Datenmengen auf einmal programmiert werden können. In der Regel ist die entgegengesetzte Operation, das Löschen, aber nur in größeren Einheiten, so genannten Sektoren (meistens ein Viertel, Achtel, Sechzehntel usw. der Gesamtspeicherkapazität) möglich. Dabei ist die logische Polarität nicht immer gleich: es existieren sowohl Implementierungen, die das Programmieren logisch als Übergang logisch ‚0‘ nach ‚1‘ realisieren, als auch umgekehrt.

Gemeinsames Merkmal ist aber immer, dass die beiden Operationen

- jeweils nur den Übergang in eine Richtung (‚0‘ nach ‚1‘ oder ‚1‘ nach ‚0‘) darstellen und

- (oft) nur eine von beiden bit-selektiv arbeiten kann: das Programmieren.

Das bedeutet, dass zum Wiederbeschreiben immer erst eine Löschoperation (auf einem Byte bei manchen EEPROM-Architekturen, auf einem Sektor bei Flash) nötig ist und dann das gewünschte Bit-Pattern, also der gewünschte Speicherinhalt durch Programmieroperationen hergestellt wird.

Oft müssen zum Schreiben auf den Flash-Speicher spezielle Kommandos (in Form einer Sequenz von anzulegenden genau spezifizierten Daten-/Adresspaaren) an den Flash-Speicher gegeben werden. Das ist eine Sicherheitsmaßnahme gegen unbeabsichtigtes Beschreiben oder Löschen des Speichers.

All diese Detailoperationen geschehen in der Regel transparent für den Benutzer und das jeweilige Anwendungsprogramm. Meistens gibt es für Flash-Speicher optimierte Dateisysteme, die diese Verfahrensweisen implementieren. Manche Flash-Speicher wie beispielsweise USB-Sticks tragen auch zur Bedienung der Schnittstelle zum Rechner einen eigenen Mikrocontroller und bringen solche Dateisysteme als Treiber in dessen ROM mit.

Architekturen

Am Markt sind derzeit zwei Flash-Architekturen gängig, die sich in der Art der internen Verschaltung der Speicherzellen und damit in der Speicherdichte und Zugriffsgeschwindigkeit unterscheiden. Grundsätzlich sind die Speicherzellen als Matrix angeordnet, wobei über eine Achse die Adressleitungen zur Auswahl einer Spalte bzw. Zeile von Speicherzellen dienen und in der anderen Achse Datenleitungen zu den Speicherzellen führen. Die Realisierung der Datenleitungen stellt den wesentlichen Unterschied zwischen den Architekturen NAND-Flash und NOR-Flash dar.

NAND-Flash

- → Hauptartikel: NAND-Flash

Die Speicherzellen sind in größeren Gruppen (z. B. 1024) hintereinander geschaltet (Serienschaltung). Das entspricht dem n-Kanal-Zweig eines NAND-Gatters in der CMOS-Technologie. Eine Gruppe teilt sich jeweils eine Datenleitung. Lesen und Schreiben ist dadurch nicht wahlfrei möglich, sondern muss immer in ganzen Gruppen sequentiell erfolgen. Durch die geringere Zahl an Datenleitungen benötigt NAND-Flash weniger Platz. Da Daten auch auf Festplatten blockweise gelesen werden, eignet sich NAND-Flash trotz dieser Einschränkung als Ersatz der Plattenspeicher.

Die NAND-Architektur zielt auf Märkte, in denen es auf viel Speicher auf wenig Raum ankommt, weniger jedoch auf geringe Zugriffszeit auf ein beliebiges Datum. Die NOR-Architektur setzt auf den Ersatz von UV-löschbaren EPROMs (die zwischenzeitlich von Flash-Bausteinen nahezu ersetzt sind und kaum noch weiterentwickelt werden). Außerdem lassen sich hier erheblich kürzere Zugriffszeiten realisieren: die Parallelschaltung hat den geringeren Widerstand zwischen Stromquelle und Auswerteschaltung.

NOR-Flash

- → Hauptartikel: NOR-Flash

Die Speicherzellen sind über Datenleitungen parallel geschaltet – diese können je nach genauer Architektur auf der Source- oder der Drain-Seite liegen. Das entspricht einer Verschaltung wie im n-Kanal-Zweig eines NOR-Gatters in CMOS. Der Zugriff kann hier wahlfrei und direkt erfolgen. Deshalb wird der Programmspeicher von Mikrocontrollern aus NOR-Flash aufgebaut.

Nachteile beider Architekturen

Flash-Speicher haben eine begrenzte Lebensdauer, die in einer maximalen Anzahl an Lösch-Zyklen angegeben wird (10.000 bis 100.000 Zyklen für NOR-Flash und bis zu 2 Million für NAND-Flash). Dies entspricht gleichzeitig der maximalen Anzahl Schreib-Zyklen, da der Speicher jeweils blockweise gelöscht werden muss, bevor er wiederum beschrieben werden kann. Diese Zyklenzahl wird Endurance genannt. Verantwortlich für diese begrenzte Lebensdauer ist das Auftreten von Schäden in der Oxidschicht im Bereich des Floating-Gates, was das Abfließen der Ladung bewirkt.[2]

Eine andere wichtige Kenngröße ist die Zeit der fehlerfreien Datenhaltung, die Retention.

Ein weiterer Nachteil ist, dass der Schreibzugriff bei Flash-Speicher erheblich langsamer erfolgt als der Lesezugriff. Zusätzliche Verzögerungen können dadurch entstehen, dass immer nur ganze Blöcke gelöscht werden können.

Technologien

Das wichtigste Kriterium zur Unterscheidung von Flashtechnologien ist natürlich die Geometrie der Speicherzelle, des Flashtransistors, u. a. werden folgende Zelltypen unterschieden (dabei können mehrere der nachfolgenden Merkmale zugleich zutreffen):

- die Split-Gate-Zelle, s. Abb.

- die ETOX-Zelle, eine vereinfachte Struktur, bei der der nach unten abknickende Teil des Steuer-Gates der Split-Gate-Zelle entfällt, deren Floating-Gate in aller Regel mit CHE geladen wird

- die UCP-Zelle, die i. d. R. in beiden Richtungen mit Fowler-Nordheim-Tunneling beschrieben wird

- die NROM-Zelle ohne eigentliches Floating-Gate: hier wird die Ladung direkt in eine Zone des Isolators zwischen Kanal und Steuer-Gate 'geschossen', auch in Ausführungen, bei denen zwei Ladungszonen (eine in Source-, die andere in Drain-Nähe) ausgeprägt werden, wodurch diese Zelle zwei Bit auf einmal speichern kann.

- die 2-Transistorzelle: ein normaler n-Kanal-Transistor und ein Flashtransistor hintereinander. Diese Zelle hat den Nachteil, dass sie größer ist, aber u. U. für Programmieren und Löschen einfacher ansteuerbar ist, was bei kleineren Speichergrößen in anderen Schaltungsteilen Flächeneinsparungen bringen kann.

- Multi-Level-Zelle: Hier speichert die Flash-Zelle nicht nur ein Bit, sondern (meist) 2, inzwischen auch 4[3] voneinander unabhängige Bitzustände. Diese werden in Leitfähigkeitswerte kodiert, die in der Ausleseelektronik wieder auf die beiden Bits verteilt werden. Der faktischen Verdopplung der Speicherkapazität steht aber die deutlich verlängerte Zugriffszeit (es muss eine analoge Spannung auf vier Niveaus gegenüber nur zwei bei den binären Flash-Zellen überprüft werden) und eine größere Fehlerwahrscheinlichkeit (eine Leitfähigkeitsänderung um ein Viertel des maximalen Leitfähigkeitsunterschied kann bereits den Wert des in der Zelle gespeicherten Niveaus verändern) entgegen.

Speichergrößen

Anfang 2009 liefern mehrere Hersteller (Samsung, Toshiba und andere) NAND-Flash-Speicher mit 16 Gigabit in SLC-Technologie (Single Level Cell) und 32 Gigabit in MLC-Technologie (Multi Level Cell), NOR-Flash-Speicher erreicht zur gleichen Zeit 1 Gigabit Speicherkapazität.

Der Unterschied in der Speicherkapazität rührt vor allem daher, dass bei NAND-Flash-Speicher die Daten- und Adress-Leitungen auf denselben Anschlüssen (Pins) ausgeführt werden, d. h. derselbe Anschluss abwechselnd für Daten- und Adressübermittlung genutzt wird („Multiplex“), während bei den NOR-Flash-Speichern diese getrennt sind. Dadurch können die NOR-Typen wesentlich schneller bei den Datenzugriffen sein, haben aber bedeutend mehr Pins und bedürfen damit prinzipiell größerer Gehäuse. De facto sind jedoch bei hohen Kapazitäten die Gehäuse der NAND-Typen nahezu genauso groß wie jene der NOR-Typen, was aber an dem sehr großen Speicherchip im Innern, nicht am Platzbedarf der Anschlüsse liegt. Dennoch sind die wenigsten Gehäusepins bei NAND-Typen tatsächlich angeschlossen, der Vorteil der simpleren „Verdrahtung“ des Bausteins im Gerät bleibt deshalb erhalten.

Anzahl der Löschzyklen

Die Anzahl der Löschzyklen von NAND-Flash-Speichern ist nicht genau zu ermitteln. Laut den Herstellern betragen diese 100.000 bis 2.000.000 (Stand 2008). Bei NOR-Flash-Typen beträgt die zugesicherte Anzahl nur etwa 10.000. Jedoch geben die Hersteller an, dass ihre Speicher auch das Zehnfache schaffen. Bei einem Test der Computerzeitschrift c’t wurde ein USB-Stick 16 Millionen Mal beschrieben (immer auf dieselbe Datei), ohne dass ein Fehler auftrat. Dies setzt jedoch ein gutes Defektmanagement des Sticks voraus.

Der Flash-Speicher speichert seine Informationen auf dem Floating-Gate. Bei einem Löschzyklus durchtunneln die Elektronen die Oxidschicht. Dafür sind hohe Spannungen erforderlich. Dadurch wird bei jedem Löschvorgang die Oxidschicht, die das Floating-Gate umgibt, ein klein wenig beschädigt (Degeneration). Irgendwann ist die Isolation durch die Oxidschicht nicht mehr gegeben und die Elektronen bleiben nicht mehr auf dem Floating-Gate gefangen und die auf der Speicherzelle gespeicherte Information geht verloren. Der Defekt einer einzelnen Zelle macht einen Flash-Speicher noch lange nicht unbrauchbar.

Defektmanagement im Flash/Ansteuerlogik

Ausfälle einzelner Zellen werden durch eine Fehlererkennung erkannt und in einem geschützten Bereich protokolliert. Für die Fehlererkennung und -korrektur werden zu jedem Block (512 Byte) zusätzliche Bits gespeichert. Mit diesen Schutzbits sind einzelne fehlerhafte Bits korrigierbar, Fehler über mehrere Bits werden nur erkannt. Die Ansteuerlogik zeigt Fehler dieses Blocks an, die Treibersoftware kann dann diese Blocks als defekt markieren. Diese Defekttabelle befindet sich im sogenannten Spare-Bereich des Flash, der im normalen Betrieb nicht beschrieben wird. Die Berechnung und Kontrolle der Schutzbits wird in der Ansteuerlogik, nicht im Flash selbst realisiert, dabei kommt oft ein Hamming-Code zur Anwendung.

Defektmanagement durch Software

Um solche Defekte zu vermeiden, wird die Treibersoftware (ein spezielles Dateisystem) so ausgelegt, dass sie die Schreib- und Löschaktionen möglichst gleichmäßig über den gesamten Speicherbereich eines Bausteins verteilt und beispielsweise nicht einfach immer bei Adresse 0 anfängt zu schreiben. Man spricht dabei von Wear-Leveling-Algorithmen.

Vorteile

- Datenerhalt bei fehlender Versorgungsspannung (nichtflüchtiger Speicher/nonvolatile Memory)

- geringer Energieverbrauch im Betrieb

- geringe Wärmeentwicklung im Betrieb

- Auslesen funktioniert bei NOR-Typen genauso wie bei herkömmlichen statischen RAM-Bausteinen

- resistent gegen Erschütterungen und magnetische Felder

- kleine Bauform

- geringes Gewicht

- geräuschlos

- bei Parallelbetrieb sind fast beliebige Lese- und Schreibgeschwindigkeiten und über das Medium weitgehend konstante erreichbar

- sehr hohe Datendichte (eine 16 GB-microSD-Karte erreicht inklusive Plastikgehäuse und Controller 139 GB/cm³)

- im Vergleich zu Festplatten sehr kurze Zugriffszeiten

- Haltbarkeit der Daten, weil keine beweglichen Teile und keine Empfindlichkeit gegen Luftfeuchtigkeit

Nachteile

- Ist derzeit noch deutlich teurer als Festplatten und optische Speichermedien, jedoch besteht ein starker Preisverfall. Windows Vista nutzt Flash-Speicher deshalb als ReadyBoost-Cache. Hiervon verspricht man sich eine Beschleunigung häufig benötigter Funktionen, wie beispielsweise des Betriebssystems. Untersuchungen der Fachzeitschrift c’t[4] belegen jedoch, dass dies in der Praxis so nicht eintritt.

- langsamer als RAM (Random Access Memory), vor allem beim Schreiben

- es können (oft) nur ganze Sektoren auf einmal gelöscht werden. Allerdings sorgen entsprechende Algorithmen dafür, dass zyklisch der gesamte Speicherplatz beschrieben wird, bevor irgendein Speicherbereich ein weiteres Mal genutzt wird. Gemäß der Fachzeitschrift c't[4] war es in einem Dauertest nicht möglich, USB-Sticks kaputt zu flashen, wenn man einen Festplatteneinsatz über viele Jahre simulierte. Ähnlich gelagerte Algorithmen[5] führen zu einem Ersatz von EEPROMs durch Flashs. Hierzu wird beim Schreiben ein Datensatz aus Adresse und Datum des zu emulierenden EEPROMs in einem Flash abgespeichert. Beim erneutem Schreiben auf die gleiche Speicherzelle des EEPROMs wird ein neuer Datensatz in die nächste freie Speicherzelle geschrieben. Immer nur der letzte Eintrag unter einer gleichen Adresse wird beim Lesen als gültig erachtet und kann über einen schnellen Suchalgorithmus, zum Beispiel mit der binären Suche mit einem Aufwand von nur log2 (Speicherzellen/Page) Suchschritten gefunden werden. Dies geht bei modernen Microcontrollern im statistischen Mittel immer noch schneller, als ein etwa 10-mal so langsames EEPROM zu nutzen. Auch hier wird durch ein vollständiges Beschreiben des gesamten Speicherraumes vor einem erneuten Zyklus dafür gesorgt, dass die Lebensdauer des Flashs diejenige des EEPROMs im statistischen Mittel übersteigt. In neueren Controllern wird daher bei größeren Speichern auf das EEPROM verzichtet. In allernächster Zukunft werden die EEPROMs durch Flashs ersetzt werden können, auf denen der beschriebene Emulationsvorgang in Hardware gegossen stattfindet.

- relativ komplexe Ansteuerung beim Schreiben/Löschen (Memory Controller erforderlich, z. T. werden Flash-Speicher sogar mit eigenen intelligenten Interfaces ausgestattet)

- grundsätzlich begrenzte Anzahl von Schreibzyklen (schon beim Annähern an diese Grenze steigende Unzuverlässigkeit, die aber durch bekannte Korrekturverfahren eliminiert werden kann und in einigen Produkten auch eliminiert wird)[2]

- um bei NOR-Typen eine Zuverlässigkeit vergleichbar der von SRAM-Bausteinen zu erreichen, müssen in der Regel innerhalb des Bausteins Schaltkreise für eine Fehlerkorrektur (zum Beispiel ECC-64) vorgesehen werden.

- bei noch größeren Kapazitäten in der Größenordnung von Festplattenspeicher (meist mit NAND-Chips realisiert) wird oft der Einsatz von Ersatzsektoren nötig, um trotz sektorweiser Fehlerkorrektur komplett ausgefallene Sektoren zu ersetzen.

Einzelnachweise

- ↑ P. Pavan, R. Bez, P. Olivo, E. Zanoni: Flash Memory Cells - An Overview. In: Proceedings of the IEEE. 85, Nr. 8, 1997, ISSN 0018-9219, S. 1248–1271 (doi:10.1109/5.622505) (PDF (500 kB)).

- ↑ a b Benjamin Benz: Erinnerungskarten – Die Technik der Flash-Speicherkarten. In: c’t. Nr. 23, 2006, ISSN 0724-8679 (Leseprobe).

- ↑ Christof Windeck: MirrorBit Quad: Vier Bits pro Flash-Speicherzelle. In: Heise-Online. 26. Sep. 2006. Abgerufen am 27. März 2009.

- ↑ a b Benjamin Benz, Boi Feddern: Festplatte ade –Wie Flash-Speicher allmählich den PC erobert. In: c’t. Nr. 21, 2007, ISSN 0724-8679 (Leseprobe).

- ↑ David Otten, Stephen Cowden: Emulating Data EEPROM for PIC18 and PIC24 MCUs and dsPIC DSCs. Algorithmus zum Ersatz von EEPROM durch Flash-Speicher. Microchip Technology, 5. Aug. 2008 (Online ; Anwendungshinweise AN1095).

Literatur

- Boi Feddern, Benjamin Benz: Speicherkarten/FAQ – Flash-Haltbarkeit. In: c’t. Nr. 2., 2007, ISSN 0724-8679.

Weblinks

- Algorithmus zum Ersatz von EEPROM durch Flash Speicher (englisch)

- NAND vs. NOR Flash Memory von Toshiba (Englisch)

Wikimedia Foundation.