- Row Address Strobe

-

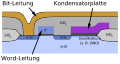

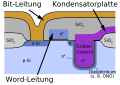

Dieser Artikel beschreibt den DRAM-Chip. Für das mit diesen Chips aufgebaute DRAM-Modul (ugs.: Speicherriegel), siehe Artikel Speichermodul. - Bei der Stapel-Technologie (engl. stack) wird der Kondensator über dem Transistor aufgebaut.

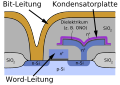

- Bei der Graben-Technologie (engl. trench) wird der Kondensator durch Ätzen eines ca. 5–10 Mikrometer tiefen Loches (oder Grabens) in das Substrat erzeugt.

- Im Ruhezustand eines DRAMs befindet sich die Wortleitung auf niedrigem Potential (UWL = 0 V). Die Zelltransistoren sind dadurch nichtleitend, die in den Kondensatoren gespeicherte Ladung bleibt - abgesehen von unerwünschten Leckströmen - erhalten.

- Beide in dem Diagramm des Zellenfeldes über den Leseverstärkern skizzierten Schalter sind geschlossen. Durch sie werden die beiden Bitleitungen welche gemeinsam an einem Leseverstärker angeschlossen sind, auf gleichem Potential (½ * UBL) gehalten.

- Die Spannungsversorgung der Leseverstärker (UBL) ist abgeschaltet.

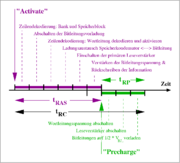

- Aus der bei einem Activate übergebenen Bank- und Zeilenadresse (vgl. Diagramme zum „Burst Read“-Zugriff) wird zunächst ermittelt in welcher Bank und ggf. in welchem Speicherblock sich die angegebene Zeile befindet.

- Die Schalter zur 'Bitleitungsvorladung' werden geöffnet. Die bis dahin auf halbe Bitleitungsspannung aufgeladenen Bitleitungen sind damit von jeder Spannungsquelle abgekoppelt.

- An die Wortleitung wird eine positive Spannung angelegt. Die Transistoren des Zellenfeldes werden somit leitend. Durch die langen Wortleitungen kann dieser Vorgang mehrere Nanosekunden andauern und ist somit einer der Gründe für die „Langsamkeit“ eines DRAMs.

- Es findet ein Ladungsaustausch zwischen dem Zellkondensator und einer der beiden an einem Leseverstärker angeschlossenen Bitleitungen statt. Am Ende des Ladungsaustausches haben sich die Zelle und Bitleitung auf eine Spannung von

-

- aufgeladen. Das Vorzeichen der Spannungsänderung (±) hängt davon ab, ob zuvor in der Zelle eine '1' oder eine '0' gespeichert war. Aufgrund der hohen Bitleitungskapazität CBL / C = 5 … 10 (bedingt durch die Leitungslänge) liegt die Spannungsänderung in einer Größenordnung von nur 100 mV. Dieser Umladungsvorgang dauert aufgrund der hohen Bitleitungskapazität ebenfalls einige Nanosekunden.

- Gegen Ende dieses Umladungsvorganges wird die Versorgungsspannung (UBL) der primären Leseverstärker eingeschaltet. Diese beginnen mit der Verstärkung des kleinen Spannungsunterschiedes zwischen beiden Bitleitungen und laden eine davon auf UBL auf und entladen die andere auf 0 V.

- Zum Lesen von Daten muss nun vom Spaltendekoder die Spaltenadresse dekodiert werden.

- Die zur Spaltenadresse korrespondierende Spaltenauswahlleitung (engl. column select line, CSL) wird aktiviert und verbindet ein oder mehrere Bitleitungen am Ausgang der primären Leseverstärker mit Datenleitungen, die aus dem Zellenfeld herausführen. Aufgrund der Länge dieser Datenleitungen müssen die Daten am Rande des Zellenfeldes erneut mit einem (sekundären) Leseverstärker verstärkt werden.

- Die ausgelesenen Daten werden in ein Schieberegister parallel eingelesen, dort mit dem externen Takt (engl. clock) synchronisiert und verstärkt ausgegeben.

- Die in den DRAM einzuschreibenden Daten werden nahezu zeitgleich mit der Spaltenadresse eingelesen.

- Die Spaltenadresse wird vom Spaltendekoder dekodiert und die entsprechende Spaltenauswahlleitung wird aktiviert. Dadurch wird wieder die Verbindung zwischen einer Datenleitung und einer Bitleitung hergestellt.

- Parallel zur Decodierung der Spaltenadresse treffen die Schreibdaten am Spaltenauswahlblock an und werden zu den Bitleitungen weitergeführt. Die (schwachen) primären Leseverstärker werden dabei überschrieben und nehmen nun einen den Schreibdaten entsprechenden Zustand an.

- Die Leseverstärker unterstützen nun das Umladen der Bitleitungen und der Speicherkondensatoren im Zellenfeld.

- Die Wortleitungsspannung wird auf 0 V oder einen leicht negativen Wert verringert. Dadurch werden die Zelltransistoren nichtleitend und koppeln die Zellkondensatoren von den Bitleitungen ab.

- Die Spannungsversorgung der Leseverstärker kann nun abgeschaltet werden.

- Die die beiden Bitleitungen verbindenden Schalter zur Bitleitungsvorladung werden geschlossen. Damit stellt sich auf den Bitleitungen wieder der Ausgangszustand (U = ½ UBL) ein.

- RAS-only-Refresh

- Diese Methode beruht auf der Tatsache, dass das Aktivieren einer Zeile automatisch mit einer Bewertung und einem Rückschreiben des Zellinhaltes verbunden ist. Zu diesem Zweck muss der Speichercontroller extern die Zeilenadresse der aufzufrischenden Zeile anlegen und über die Steuersignale eine Aktivierung der Zeile bewirken (vgl. Diagramm zum RAS-only-Refresh beim EDO-DRAM).

- CAS-before-RAS-Refresh

- Diese Refreshmethode erhielt ihren Namen von der Ansteuerung asynchroner DRAMs, ist aber auch bei synchronen DRAMs unter der Bezeichnung Auto-Refresh erhalten geblieben. Die Namensgebung beruhte auf der ansonsten unzulässigen Signalfolge – diese Art der Signalsetzung wird in der Digitaltechnik vermieden, da sie relativ fehleranfällig ist (z. B. bei der Synchronisation) –, dass eine fallende CAS-Flanke vor einer fallenden RAS-Flanke erzeugt wurde (vgl. Diagramm zum CBR-Refresh beim EDO-DRAM). Als Reaktion auf die Signalfolge führte der DRAM einen Refreshzyklus durch, ohne dass er auf eine externe Adresse angewiesen war. Stattdessen wurde die Adresse der aufzufrischenden Zeile in einem internen Zähler bereitgestellt und nach erfolgter Ausführung automatisch erhöht.

- Self-Refresh

- Diese Methode war bei speziellen Bauformen asynchroner DRAMs eingeführt worden und wurde erst mit synchronen DRAMs verbindlich implementiert. Bei dieser Methode wird weitestgehend auf externe Steuer- oder Adresssignale (für den Refresh) verzichtet (vgl. Diagramm zum Self-Refresh beim EDO-DRAM). Der DRAM befindet sich dabei in einem Stromsparzustand (power-down), in dem er auf externe Signale nicht reagiert (eine Ausnahme stellen natürlich die Signale dar, die ihm das Verbleiben im Stromsparzustand anzeigen). Zum Erhalt der gespeicherten Information wird ein DRAM-interner Zähler verwendet, der in vorgegebenen Zeitabständen einen Auto-Refresh (CAS-before-RAS-Refresh) initiiert. In neueren DRAMs (DDR-2, DDR-3) wird die Periode für den Refresh meist temperaturabhängig geregelt (als sogenannter Temperature Controlled Self-Refresh, TCSR), um den Betriebsstrom im Self-Refresh bei niedrigen Temperaturen zu reduzieren.

- beim Single-Data-Rate(SDR)-SDRAM wird pro Leseanforderung 1 Datenbit pro Datenpin ausgelesen: Prefetch = 1

- beim DDR-SDRAM werden pro Leseanforderung 2 Datenbits pro Datenpin ausgelesen und in einem Datenburst der Länge 2 ausgegeben: Prefetch = 2

- beim DDR2-SDRAM werden pro Leseanforderung 4 Datenbits pro Datenpin ausgelesen und in einem Datenburst der Länge 4 ausgegeben: Prefetch = 4

- beim DDR3-SDRAM werden pro Leseanforderung 8 Datenbits pro Datenpin ausgelesen und in einem Datenburst der Länge 8 ausgegeben: Prefetch = 8

- Mit Hilfe eines fokussierten Laserpulses werden entsprechend vorbereitete Kontakte in den Dekodierungschaltungen der Zeilen- oder Spaltenadresse verdampft (laser-fuse).

- Mit Hilfe eines elektrischen Überspannungspulses werden elektrische Kontakte entweder geöffnet (e-fuse) oder (z. B. durch Zerstören einer dünnen isolierenden Schicht) geschlossen (anti e-fuse).

- Christof Windeck: Riegel-Reigen: Aufbau aktueller Speichermodule. In: c’t Nr. 7, 2006, S. 238 (Kostenpflichtiger Download des Zeitschriftenartikels)

- Siemens AG (Hrsg.): Memory Components Data Book. München 1994.

- Deutsch

- MRAM/PRAM-Memory Speicher – News und Infos über die MRAM-Speicher-Technologie

- Kompakter Arbeitsspeicher dank Z-RAM – Artikel von heise online, vom 15. August 2007

- Englisch

- Memory 1997 (PDF, ca. 167 kB) – Dokument von Integrated Circuit Engineering Corporation, ISBN 1-877750-59-X

- Section 7. DRAM Technology (PDF, ca. 770 kB) – 7. Kapitel von „Memory 1997“

- The evolution of IBM CMOS DRAM Technology – Artikel von IBM, vom 25. Juli 1994

Dynamic Random Access Memory (DRAM), oder der halb eingedeutschte Begriff Dynamisches RAM, bezeichnet eine Technologie für einen elektronischen Speicherbaustein mit wahlfreiem Zugriff (Random Access Memory, RAM), der hauptsächlich in Computern eingesetzt wird, jedoch auch in anderen elektronischen Geräten wie zum Beispiel Druckern zur Anwendung kommt. Das speichernde Element ist dabei ein Kondensator, der entweder geladen oder entladen ist. Über einen Schalttransistor wird er zugänglich und entweder ausgelesen oder mit neuem Inhalt beschrieben. Der Speicherinhalt ist flüchtig (volatil), das heißt die gespeicherte Information geht bei fehlender Betriebsspannung oder zu später Wiederauffrischung verloren.

Inhaltsverzeichnis |

Einleitung

Ein Kennzeichen des DRAM ist die Kombination aus einer sehr hohen Datendichte auf einer kleinen Chipfläche, verbunden mit sehr preiswerten Herstellungskosten. Er findet deswegen vor allem dort Verwendung, wo große Speichermengen bei mittlerer Datenrate (100–1600 Mbit/s/pin) zur Verfügung gestellt werden müssen.

Diesem Vorteil des DRAM gegenüber dem SRAM steht der Nachteil gegenüber, dass sich die im Kondensator gespeicherte Ladung und damit die gespeicherte Information aufgrund von Leckströmen mit der Zeit verflüchtigt, wenn sie nicht periodisch wieder aufgefrischt wird. Dies ist normalerweise in Abständen von einigen Millisekunden erforderlich. Das Auffrischen des Speichers wird zeilenweise bewerkstelligt. Dazu wird jeweils eine Speicherzeile in einem Schritt in einen auf dem Chip befindlichen Zeilenpuffer übertragen und von dort verstärkt wieder zurück in die Speicherzeile geschrieben. Daher rührt die Bezeichnung „dynamisch“. Bei statischen Speichern wie dem SRAM kann man demgegenüber alle Signale anhalten, ohne dass Datenverlust eintritt. Das Auffrischen des DRAMs verbraucht außerdem auch im Ruhezustand eine gewisse Menge von Energie. Deshalb bevorzugt man in Anwendungen, bei denen es auf geringen Ruhestrom ankommt, das SRAM.

Die Hersteller von Speicher versuchen kontinuierlich, den Energiebedarf zu senken, um so genannte Leckströme zu minimieren. Die Versorgungsspannung von DDR2-SDRAM liegt bei 1,8 Volt, während DDR-SDRAM noch mit 2,5 Volt versorgt wird. Bei dem im Jahre 2007 eingeführten DDR3-SDRAM wurde die Spannung auf 1,5 Volt gesenkt.

Ein DRAM ist entweder als eigenständiger integrierter Schaltkreis ausgeführt oder als Speicherzelle Teil eines größeren Chips. Beispielsweise sind bei vielen Mikroprozessoren die Register als dynamische Speicherzellen ausgeführt.

Das „Random“ in Random Access Memory steht dabei für den wahlfreien Zugang auf den Speicherinhalt bzw. die einzelnen Speicherzellen, im Gegensatz zum sequenziellen Zugriff wie beispielsweise bei (hardwareseitig organisierten) FIFO- oder LIFO-Speichern.

Aufbau

Ein DRAM besteht nicht wie im Artikel Halbleiterspeicher vereinfacht gezeigt aus einer einzigen zweidimensionalen Matrix. Stattdessen sind die Speicherzellen, die auf der Oberfläche eines Dies angeordnet und verdrahtet sind, in einer ausgeklügelten hierarchischen Struktur unterteilt. Während die innere Struktur herstellerspezifisch aufgebaut ist, ist die von außen sichtbare logische Struktur vom Industriegremium JEDEC normiert. Dadurch wird sichergestellt, dass sich Chips unterschiedlicher Hersteller und verschiedener Größen nach dem immer gleichen Schema ansprechen lassen.

Aufbau einer Speicherzelle

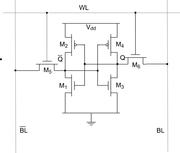

Der Aufbau einer einzelnen DRAM-Speicherzelle ist sehr einfach, sie besteht nur aus einem Kondensator und einem Transistor. Heute verwendet man einen MIS-Feldeffekttransistor. Die Information wird als elektrische Ladung im Kondensator gespeichert. Jede Speicherzelle speichert ein Bit. Während früher meist Kondensatoren in Planartechnologie Verwendung fanden, werden aktuell zwei andere Technologien verwendet:

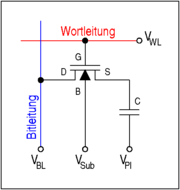

Der in der nebenstehenden Abbildung eingezeichnete obere Anschluss wird entweder auf die Bit-Leitungsspannung VBL aufgeladen oder entladen (0 V). Der untere Anschluss aller Kondensatoren wird gemeinsam an eine Spannungsquelle angeschlossen, welche idealerweise eine Spannung von VPl= 1/2 * VBL besitzt. Dadurch lässt sich die Maximalfeldstärke im Dielektrikum des Kondensators halbieren.

Der Transistor (auch Auswahltransistor genannt) dient als Schalter zum Lesen und Schreiben der Information aus der Zelle. Dazu wird über die Word-Leitung (engl. wordline) an den Gate-Anschluss „G“ des n-MOS-Transistors eine positive Spannung VWL angelegt werden. Dadurch wird eine leitende Verbindung zwischen den Source- („S“) und den Drain-Gebieten („D“) hergestellt, welche den Zellkondensator mit der Bit-Leitung (engl. bitline) verbindet. Der Substrat-Anschluss „B“ (bulk) des Transistors ist entweder an das Massepotential oder an ein leicht negatives Potential VSub zur Unterdrückung von Leckströmen angeschlossen.

Durch ihren sehr einfachen Aufbau brauchen die Speicherzellen nur sehr wenig Chipfläche. Die konstruktionsbedingte Größe einer Speicherzelle wird gern als das Vielfache der Quadratfläche F² der kleinsten fertigbaren Strukturlänge („minimum Featuresize“ oder abgekürzt F) angegeben: Eine DRAM-Zelle benötigt heute 6 oder 8 F², während eine SRAM-Zelle mehr als 100 F² benötigt. Daher kann ein DRAM bei gegebener Chipgröße eine wesentlich größere Zahl von Bits speichern. Daraus resultieren weitaus niedrigere Herstellungskosten pro Bit als beim SRAM. Unter den heute üblichen elektronischen Speicherarten hat nur der NAND-Flash eine kleinere Speicherzelle mit ungefähr 4,5 F² (bzw. 2,2 F² pro Bit für Multilevel-Cells).

Aufbau einer Speicherzeile („Page“)

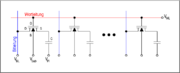

Durch Anschließen weiterer Speicherzellen an eine Wortleitung erhält man eine Speicherzeile, die üblicherweise als Seite (engl. page) bezeichnet wird. Das Charakteristische an einer Zeile ist die Eigenschaft, dass alle zugehörigen Zellen bei der Aktivierung einer Wortleitung (rot dargestellt) ihren gespeicherten Inhalt gleichzeitig auf die ihnen zugeordnete Bitleitung (blau dargestellt) ausgeben. Eine übliche Pagegröße liegt bei 1 K, 2 K, 4 K (…) Zellen (1 K = 1024).

Aufbau eines Zellenfeldes

Die Speicherzellen sind in einer Matrixanordnung verschaltet: 'Wortleitungen' verbinden alle Steuerelektroden der Auswahltransistoren in einer Zeile, Bitleitungen verbinden alle Drain-Gebiete der Auswahltransistoren einer Spalte.

Am unteren Rande der Matrix sind die Bitleitungen mit den (primären) Schreib-/Lese-Verstärkern (engl. sense-amplifier) verbunden. Da sie in das enge Raster des Zellenfeldes passen müssen, sind sie in der einfachsten Form als zwei gegengekoppelte CMOS-Inverter aus nur vier Transistoren aufgebaut. Ihre Versorgungsspannung ist gerade gleich der Bitleitungsspannung VBL. Neben ihrer Funktion als Verstärker des ausgelesenen Zellsignals haben sie noch den Nebeneffekt, dass ihr Aufbau dem eines einfachen statischen Speichers (Latch) entspricht. Der primäre Leseverstärker dient somit gleichzeitig als Speicher einer kompletten Speicherzeile.

Die über den Leseverstärkern eingezeichneten Schalter dienen im inaktiven Zustand zur Vorladung der Bitleitungen auf einen Pegel von ½ · VBL, welcher gerade den Mittelwert der Spannung einer aufgeladenenen und einer entladenen Zelle darstellt.

Auf einem Speicher-Chip sind eine Vielzahl dieser Speichermatrizen zu einem zusammenhängenden Speicherbereich verschaltet, der Chip ist also (transparent nach außen) intern in Submatrizen gegliedert. Dabei werden je nach Auslegung sämtliche Datenleitungen zu einem einzigen Datenpin nach außen geführt oder auf 4, 8 (selten), 16 oder 32 (DRAMs für Graphikanwendungen) Datenpins verteilt. Dies ist dann die Datenbreite des einzelnen DRAM-Chips. Je nach ihrem Wert braucht man z. B. 8, 2 oder 1 Chip(s) für eine Datenbusbreite von 8 Bit bzw. das Vierfache davon für 32 Bit und das Achtfache für 64 Bit.

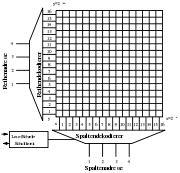

Adressdekodierung

Das benachbart abgebildete Diagramm zeigt den prinzipiellen Aufbau der Adressdekodierung für ein einzelnes Zellenfeld. Die Zeilenadresse wird über n Adressleitungen dem Zeilendekoder zugeführt. Dieser wählt aus den an ihn angeschlossenen 2n Wortleitungen genau eine einzelne aus und aktiviert diese, indem er ihr Potential auf die Wortleitungsspannung VWL anhebt. Die dadurch im Zellenfeld aktivierte Speicherzeile gibt ihren Dateninhalt nun auf die Bitleitungen aus. Das resultierende Signal wird von den (primären) Leseverstärkern verstärkt, gespeichert und gleichzeitig wieder in die Zelle zurückgeschrieben.

Die Dekodierung der Spaltenadresse und die Auswahl der auszulesenden Daten ist ein zweistufiger Prozess. In einem ersten Schritt werden die m Adressleitungen der Spaltenadresse dem Spaltendekoder zugeführt. Dieser wählt aus den üblicherweise 2m angeschlossenen Spaltenauswahlleitungen eine aus und aktiviert diese. Damit werden je nach Breite des Speichers k Bitleitungen gleichzeitig ausgewählt. In einem zweiten Schritt wird im Block Spaltenauswahl diese Untermenge von k Bitleitungen aus der Menge der insgesamt k · 2m Bitleitungen mit den k Datenleitungen Richtung Außenwelt verbunden. Diese werden abschließend von einem weiteren Schreib-/Leseverstärker (nicht eingezeichnet) verstärkt.

Um das Übersprechen zwischen benachbarten Speicherzellen und ihren Zuleitungen zu begrenzen, werden die Adressen bei der Dekodierung üblicherweise verwürfelt, und zwar nach einer standardisierten Regel, so dass sie nicht in der Reihenfolge ihrer binären Wertigkeit in der physischen Anordnung wiederzufinden sind.

Interne Abläufe

Ausgangszustand

Aktivierung einer Speicherzeile

Lesen von Daten

Schreiben von Daten

Deaktivierung einer Speicherzeile

Timingparameter der internen Abläufe

tRCD

Der Parameter tRCD (RAS-to-CAS delay, row-to-column delay) beschreibt bei einem DRAM die Zeit, die nach der Aktivierung einer Wortleitung (Activate) verstrichen sein muss, bevor ein Lesekommando (Read) gesendet werden darf. Der Parameter ist dadurch bedingt, dass das Verstärken der Bitleitungsspannung und das Rückschreiben des Zellinhaltes abgeschlossen sein muss, bevor die Bitleitungen mit den Datenleitungen weiterverbunden werden dürfen.

CL

Der Parameter CL (CAS Latency, auch tCL) beschreibt die Zeit, welche zwischen der Absendung eines Lesekommandos und dem Erhalt der Daten vergeht.

Siehe auch: Column Address Strobe Latency

tRAS

Der Parameter tRAS (RAS pulse width, Active Command Period, Bank Active Time) beschreibt die Zeit, die nach der Aktivierung einer Zeile (bzw. einer Zeile in einer Bank) verstrichen sein muss, bevor ein Kommando zum Deaktivieren der Zeile (Precharge, Schließen der Bank) gesendet werden darf. Der Parameter ist dadurch gegeben, dass die Verstärkung der Bitleitungsspannung und das Rückschreiben der Information in die Zelle vollständig abgeschlossen sein muss, bevor die Wortleitung deaktiviert werden darf.

tRP

Der Parameter „tRP“ („Row Precharge Time“) beschreibt die Zeit, die nach einem Precharge-Kommando mindestens verstrichen sein muss, bevor ein erneutes Kommando zur Aktivierung einer Zeile in der gleichen Bank gesendet werden darf. Diese Zeit ist durch die Bedingung definiert, dass alle Spannungen im Zellenfeld (Wortleitungsspannung, Versorgungsspannung der Leseverstärker) abgeschaltet sind und die Spannungen aller Leitungen (insbesondere die der Bitleitungen) wieder auf ihrem Ausgangsniveau angekommen sind.

tRC

Der Parameter „tRC“ („Row Cycle Time“) beschreibt die Zeitdauer, die zwischen zwei aufeinander folgenden Aktivierungen zweier beliebiger Zeilen in derselben Bank verstrichen sein muss. Der Wert entspricht weitgehend der Summe der Parameter tRAS und tRP und beschreibt somit die minimal notwendige Zeit, um eine Speicherzeile aufzufrischen.

DRAM-spezifische Eigenschaften

Adressmultiplex

Adressierung

Die Adressleitungen eines DRAMs sind üblicherweise gemultiplext, d. h., es sind nur etwa halb so viele physisch vorhanden wie insgesamt benötigt werden. (Dagegen wird bei SRAMs zwecks höherer Geschwindigkeit meist der komplette Adressbus an Pins geführt, so dass der Zugriff in einer einzigen Operation erfolgen kann.)

Asynchrone DRAMs (EDO, FPM) besitzen zwei Eingangspins RAS (Row Address Select / Strobe) und CAS (Column Address Select / Strobe), um die Benutzung der Adressleitungen zu definieren: bei einer fallenden Flanke von RAS wird die an den Adressleitungen anliegende Adresse als Zeilenadresse interpretiert, bei einer fallenden Flanke von CAS wird sie als Spaltenadresse interpretiert.

RAS

Row Address Strobe, dieses Steuersignal liegt während einer gültigen Zeilenadresse an. Der Speicherbaustein legt diese Adresse in einem Zwischenspeicher ab.

CAS

Column Address Strobe, dieses Steuersignal liegt während einer gültigen Spaltenadresse an. Der Speicherbaustein legt diese Adresse in einem Zwischenspeicher ab.

Synchrone DRAMs (SDRAM, DDR-SDRAM) besitzen ebenfalls die Steuereingänge RAS und CAS, jedoch haben sie hier ihre unmittelbare Funktion verloren. Stattdessen werden bei synchronen DRAMs die Kombination aller Steuersignale (CKE, RAS, CAS, WE, CS) bei steigender Clock-Flanke ausgewertet um zu entscheiden, ob und in welcher Form die Signale auf den Adressleitungen interpretiert werden müssen.

Dem Vorteil der Einsparung von externen Adressleitungen steht ein scheinbarer Nachteil in Form einer verzögerten Verfügbarkeit der Spaltenadresse gegenüber. Die Spaltenadresse wird jedoch erst nach der Dekodierung der Zeilenadresse, der Aktivierung einer Wortleitung und dem Bewerten des Bitleitungssignals benötigt. Dieser interne Vorgang benötigt jedoch ca. 15 ns, so dass sich die verzögert erhaltene Spaltenadresse nicht negativ auswirkt.

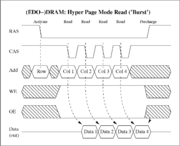

Burst

In den nebenstehenden Bildern ist für einen asynchronen und einen synchronen DRAM jeweils ein Lesezugriff im sogenannten Burst-Modus dargestellt. Das charakteristische Element eines Burst-Zugriffs (beim Lesen oder Schreiben) ist die unmittelbare Aufeinanderfolge der Daten (Data1, …, Data4). Die Daten gehören zur gleichen Zeile des Zellenfeldes, besitzen dadurch die gleiche Zeilenadresse (engl. row), aber unterschiedliche Spaltenadressen (Col1, …, Col4). Die benötigte Zeitdauer für die Bereitstellung des nächsten Datums innerhalb des Bursts ist sehr gering verglichen mit der Zeitdauer für die Bereitstellung des ersten Datums gemessen ab der Aktivierung der Zeile.

Während bei asynchronen DRAMs noch alle Spaltenadressen innerhalb des Bursts angegeben werden mussten (Col1, …, Col4), wird bei synchronen DRAMs (SDR, DDR) nur noch die Startadresse angegeben. Die für den restlichen Burst benötigten Spaltenadressen werden danach durch einen internen Zähler erzeugt.

Die hohe Datenrate innerhalb eines Bursts erklärt sich dadurch, dass innerhalb eines Bursts nur noch lesend (oder schreibend) auf die Leseverstärker zugegriffen werden muss. Die aus 2 CMOS-Invertern (4 Transistoren) aufgebauten Leseverstärker entsprechen dem Grundaufbau der Zelle eines statischen RAMs (vgl. nebenstehende Diagramme). Zur Bereitstellung des nächsten Burst-Datums ist somit lediglich die Spaltenadresse zu dekodieren und die entsprechende Spaltenauswahlleitung zu aktivieren (diese korrespondiert mit den Anschlussleitungen zum Gate-Anschluss der Transistoren M5 und M6 einer SRAM-Zelle).

Refresh

Die in kurzen Zeitabständen notwendige Wiederauffrischung (von engl.: refresh; zu dt.: auffrischen) des Speicherinhalts wird allgemein mit dem englischen Terminus Refresh bezeichnet. Die Notwendigkeit ergibt sich aus dem Auftreten unerwünschter Leckströme, welche die in den Kondensatoren gespeicherte Ladungsmenge verändern. Die Leckströme besitzen eine exponentielle Temperaturabhängigkeit: die Zeit, nach der der Inhalt einer Speicherzelle nicht mehr korrekt bewertet werden kann (retention time), halbiert sich jeweils bei einer Temperaturerhöhung um 15 bis 20 °C. Kommerziell erhältliche DRAMs besitzen meist eine vorgeschriebene Refreshperiode von 32 ms oder 64 ms.

Technisch sind dazu im Speicherchip die primären Leseverstärker (siehe Abbildung oben) mit der Funktion eines Latch-Registers ausgestattet. Sie sind als SRAM-Zellen ausgeführt, also als Flip-Flops. Wenn eine bestimmte Zeile (engl.: page; zu dt.: Seite) ausgewählt wurde, wird die komplette Zeile in die Latches des Leseverstärkers kopiert. Da die Ausgänge des Verstärkers gleichzeitig auch mit dessen Eingängen verbunden sind, werden die verstärkten Signale direkt wieder in die dynamischen Speicherzellen der ausgewählten Zeile zurückgeschrieben, sie sind damit aufgefrischt.

Es gibt verschiedene Verfahren dieser Refresh-Steuerung:

Je nach Schaltungsumgebung muss für den Refresh der Normalbetrieb unterbrochen werden, zum Beispiel kann der Refresh in einer regelmäßig aufgerufenen Interrupt-Routine ausgelöst werden. Sie kann beispielsweise mit einer eigenen Zählvariablen einfach irgendeine Speicherzelle in der jeweiligen Zeile auslesen und damit diese Zeile auffrischen. Andererseits gibt es auch Situationen (vor allem in Videospeichern), in denen der gesamte Speicherbereich sowieso in kurzen Abständen angesprochen wird, so dass gar kein separater Refresh-Betrieb stattfinden muss. Manche Mikroprozessoren wie der Z80 oder aktuelle Prozessor-Chipsätze erledigen den Refresh vollautomatisch.

Bank

Vor der Einführung synchroner DRAMs musste ein Speichercontroller warten, bis die Informationen einer aktivierten Zeile zurückgeschrieben waren und die zugehörige Wortleitung deaktiviert war. Es konnte jeweils nur genau eine Zeile im DRAM aktiviert sein. Da die Länge eines kompletten Schreib- oder Lesezyklusses (row cycle time, tRC) etwa 80 ns betrug, war der Zugriff auf Daten verschiedener Zeilen recht zeitaufwändig.

Mit der Einführung synchroner DRAMs wurden zunächst 2 (16 M SDRAM), dann 4 (64 M SDRAM, DDR-SDRAM), 8 (DDR-3 SDRAM) oder sogar 16 und 32 (RDRAM) Speicherbänke eingeführt. Speicherbänke zeichnen sich dadurch aus, dass sie jeweils eigene Adressregister und Leseverstärker besitzen, so dass nun jeweils pro Bank eine Zeile aktiviert sein konnte. Durch den gleichzeitigen Betrieb mehrerer Bänke kann man hohe Latenzzeiten vermeiden, denn während eine Bank gerade Daten liefert, darf der Speichercontroller bereits Adressen für eine andere Bank senden.

Prefetch

Die im Vergleich zu einem SRAM deutlich geringere Geschwindigkeit eines DRAMs liegt in der Struktur und Funktionsweise des DRAMs begründet. (Lange Wortleitungen müssen aufgeladen werden, eine ausgelesene Zelle kann ihre Ladung nur langsam auf die Bitleitung ausgeben, der ausgelesene Inhalt muss bewertet und zurückgeschrieben werden.) Eine Verkürzung dieser Zeiten ist zwar generell über einen intern modifizierten Aufbau möglich, jedoch würde die Speicherdichte sinken und damit der Platzbedarf und somit der Herstellungspreis ansteigen.

Stattdessen wird ein Trick angewendet, um die externe Datentransferrate zu steigern, ohne die interne Geschwindigkeit erhöhen zu müssen. Bei dem so genannten Prefetching werden pro Adressierung die Daten von mehreren Spaltenadressen ausgelesen und in einen Parallel-Seriell-Wandler (Schieberegister) geschrieben. Von diesem Puffer aus werden die Daten mit der höheren (externen) Taktrate ausgegeben. Dadurch erklären sich auch die mit synchronen DRAMs eingeführten Daten-Bursts und insbesondere ihre jeweilige minimale Burstlänge (sie entspricht gerade der Länge des als Parallel-Seriell-Wandlers eingesetzten Schieberegisters und damit dem Prefetch-Faktor):

Entsprechendes gilt für das Beschreiben des DRAMs.

Redundanz

Mit der Erhöhung der Speicherdichte (d. h. der Anzahl der Speicherzellen pro Chip) erhöht sich die Wahrscheinlichkeit, dass mindestens eine Speicherzelle eine Fehlfunktion aufweist. Um die Ausbeute an funktionsfähigen DRAMs bei der Produktion zu erhöhen, werden sogenannte redundante Elemente in das Chipdesign integriert. Dabei handelt es sich um zusätzliche Zeilen- und Spaltenleitungen mit entsprechenden Speicherzellen. Wird nun bei dem die Produktion abschließenden Test eine fehlerhafte Speicherzelle festgestellt, so wird die betroffene Wort- oder Zeilenleitung deaktiviert. An ihre Stelle tritt eine (oder mehrere) Wort- oder Zeilenleitung aus der Menge der ansonsten unbenutzten redundanten Elemente.

Um diese Konfigurationsänderung dauerhaft im DRAM abzuspeichern, bedarf es einer permanenten Schaltungsmodifikation. Zwei Verfahren sind derzeit im Einsatz:

In beiden Fällen werden diese permanenten Veränderungen benutzt, um die Adresse der zu ersetzenden Leitung und die Adresse der dafür zu verwendenden redundanten Leitung einzuprogrammieren.

Die Anzahl der in einem DRAM-Design eingebauten redundanten Elemente ist mit nur ca. 1 % überraschend gering. Mit einem höheren Anteil an redundanten Elementen könnten zwar größere Defekte (Speicherblöcke) repariert werden, jedoch wäre dies mit Nachteilen verbunden. Üblicherweise verringert sich die Anzahl der Defekte eines Speicherbauelementes mit fortschreitender Verbesserung des Fertigungsprozesses. Die dann nicht mehr benötigten redundanten Elemente würden nur noch Chipfläche beanspruchen (erhöhte Herstellungskosten), ohne eine nennenswerte Steigerung der Ausbeute zu erzielen.

Die Verwendung redundanter Elemente zur Korrektur fehlerhafter Speicherzellen darf nicht mit der aktiven Fehlerkorrektur auf der Basis von Paritätsbits oder fehlerkorrigierenden Codes verwechselt werden. Die hier beschriebene Fehlerkorrektur über redundante Elemente erfolgt in der Regel einmalig vor der Auslieferung des Speicherbauelementes an den Kunden. Nachträglich auftretende Fehler (Degradation des Bauelementes oder Übertragungsfehler im System) können damit nicht beseitigt werden.

Module

Oftmals werden ganze Speichermodule mit den eigentlichen Speicherchips verwechselt. Die Unterscheidung spiegelt sich in der Größenkennzeichnung wider: DIMMs misst man in Mega- oder Gigabyte, den einzelnen Modulchip auf dem DIMM dagegen in Giga- oder Megabit. Durch Fortschritte in der Herstellungstechnik können die Hersteller immer mehr Speicherzellen auf den einzelnen Chips unterbringen, so dass 512-MBit-Bausteine problemlos verfügbar sind. Erst durch die Zusammenschaltung von einzelnen SDRAM-Chips entsteht ein Speicherbaustein, welcher dem Standard entspricht.

Geschichte

Der erste kommerziell erhältliche DRAM-Chip war 1970 der von Intel vorgestellte Typ 1103. Er enthielt 1024 Speicherzellen (1 KB). Das Prinzip der DRAM-Speicherzelle wurde 1966 von Robert H. Dennard am Thomas J. Watson Research Center von IBM entwickelt.

Seither wurde die Kapazität eines DRAM-Chips um den Faktor 1 Million gesteigert und die Zugriffszeit auf ein Zehntel verkürzt. Heute (2008) besitzen DRAM-Chips Kapazitäten von bis zu 6 GByte und Zugriffszeiten von 8 ns. Die Produktion von DRAM-Speicherchips gehört zu den umsatzstärksten Segmenten der Halbleiterindustrie. Mit den Produkten wird spekuliert; es existiert ein Spotmarkt.

Anfangs wurden DRAM-Speicher aus einzelnen Speicherbausteinen (Chips) in DIL-Bauform aufgebaut. Für 16 KB Arbeitsspeicher (zum Beispiel im Atari 600XL oder CBM 8032) wurden 8 Speicherbausteine vom Typ 4116 gebraucht. Für 64 KB wurden 8 Bausteine vom Typ 4164 (C64-I) oder 2 Bausteine vom Typ 41464 (C64-II) gebraucht. IBM-Personal-Computer wurden anfangs mit 64 KB als minimale Speicherausstattung verkauft. Hier wurden allerdings 9 Bausteine vom Typ 4164 gebraucht; der neunte Baustein speicherte die Paritätsbits.

Bevor die SIMM-Speichermodule auf den Markt kamen, gab es zum Beispiel 80386er-Mainboards, die mit 8 MB Arbeitsspeicher bestückt werden konnten, der aus einzelnen Chips aufgebaut war. Dafür mussten 72 einzelne Chips vom Typ 411000 (1 MBit) in die Sockel gedrückt werden. Dies war eine langwierige und fehleranfällige Prozedur. Sollte dieses Mainboard mit nur 4 MB Arbeitsspeicher bestückt werden, wobei zeitweise die erheblich preiswerteren Chips vom Typ 41256 (256 KB) anstelle des Typs 411000 verwendet wurden, dann mussten sogar 144 einzelne Chips auf das Mainboard gesteckt werden: 9 Chips ergeben 256 KB, 16 solcher Gruppen mit jeweils 9 Chips ergaben 4 MB.

Dieses Mainboard entsprach allerdings nicht mehr dem AT-Formfaktor. Es war mehr als doppelt so groß wie ein Baby-AT-Mainboard und passte nur in ausgewählte BigTower-Gehäuse, die sechs oder noch mehr 5¼″-Laufwerkseinschübe halber Bauhöhe besaßen und heute nicht mehr üblich sind.

| Art | Jahr der Einführung |

|---|---|

| FPM DRAM / Fast Page Mode DRAM | 1987 |

| EDO RAM / Extended Data Output RAM | 1995 |

| SDRAM / Synchronous Dynamic Random Access Memory | 1997 |

| RDRAM / Rambus Dynamic Random Access Memory | 1999 |

| DDR-SDRAM / Double Data Rate Synchronous Dynamic Random Access Memory | 2000 |

| DDR2-SDRAM | 2004 |

| DDR3-SDRAM | 2007 |

Anwendung

Arbeitsspeicher

Normalerweise wird das DRAM in Form von Speichermodulen als Arbeitsspeicher des Prozessors benutzt. DRAMs werden häufig nach der Art der Baustein-Schnittstelle eingeteilt. In den Hauptanwendungen haben sich in zeitlicher Reihenfolge die Schnittstellentypen 'Fast Page Mode DRAM' (FPM), 'Extended Data Output RAM' (EDO), 'Synchronous DRAM' (SDR), 'Double-Data-Rate-Synchronous DRAM' (DDR) entwickelt. Die Eigenschaften dieser DRAM-Typen sind durch das 'JEDEC'-Consortium genormt. Daneben existiert parallel zu SDR/DDR die 'Rambus-DRAM'-Schnittstelle, das hauptsächlich bei Speicher für Server eingesetzt wird.

Spezialanwendungen

Spezieller RAM wird als Bild- und Texturspeicher für Grafikkarten eingesetzt, zum Beispiel GDDR3 (Graphics Double Data Rate SDRAM).

Durch die Beschränkung auf ein Spezialgebiet kann die Wiederauffrischung der Speicherzellen optimiert werden, so kann man dies zum Beispiel bei einem Bildspeicher in die Zeit des Zeilenrücklaufs legen. Auch ist es u. U. tolerierbar, wenn ein einzelnes Pixel zeitweise die falsche Farbe zeigt, man ist so nicht darauf angewiesen, auf die schlechteste Speicherzelle des Chips Rücksicht zu nehmen. Daher lassen sich - trotz gleicher Herstellungstechnologien - bedeutend schnellere DRAMs fertigen.

Für spezielle Anwendungen wurden weitere Typen entwickelt: das Graphics-DRAM (auch Synchronous Graphics RAM - SGRAM) ist zum Beispiel durch höhere Datenbreiten für den Einsatz auf Grafikkarten optimiert, wobei jedoch auf die prinzipielle Funktionsweise zum Beispiel eines DDR-DRAMs zurückgegriffen wird. Die Vorläufer des Graphics-RAM waren das Video RAM (VRAM) - ein auf Grafikanwendungen optimiertes Fast Page Mode RAM mit zwei Ports statt einem - und danach das Window RAM (WRAM), das EDO-Features und einen dedizierten Display-Port aufzuweisen hatte.

Für die Anwendung in Netzwerkkomponenten optimierte DRAM-Typen haben von verschiedenen Herstellern die Namen Network-RAM, Fast-Cycle-RAM und Reduced Latency RAM erhalten. In mobilen Applikationen, wie Mobiltelefonen oder PDAs, ist ein geringer Energieverbrauch wichtig - hierfür werden mobile DRAMs entwickelt, bei denen durch besondere Schaltungstechnik und Herstellungstechnologie die Stromaufnahme abgesenkt wird. Eine Zwitterrolle nimmt das Pseudo-SRAM (bei anderen Herstellern auch cellular RAM oder 1T-SRAM = 1-Transistor-SRAM) ein: der Speicher selbst ist ein DRAM, das sich nach außen wie ein SRAM verhält. Das wird erreicht, indem eine logische Schaltung den SRAM-typischen Zugriffsmechanismus auf die DRAM-Steuerung umsetzt und die bei dynamischen Speichern grundsätzlich notwendige regelmäßige Auffrischung der Speicherinhalte durch im Baustein enthaltene Schaltungen vorgenommen wird.

In der Anfangszeit der DRAMs, als diese oft noch in ein Keramik-DIL-Gehäuse eingebaut wurden, gab es Bastellösungen, sie als Bildsensoren für Selbstbaukameras zu benutzen. Dazu wurde der Metalldeckel auf dem Keramikgehäuse vorsichtig entfernt, darunter lag dann direkt – ohne jede Vergussmasse – der Die. Davor wurde ein Objektiv angeordnet, welches das Bild präzise auf die Die-Oberfläche abbildete. Wenn der Chip zu Beginn der Belichtung komplett mit 1 gefüllt wurde, also alle Speicherkondensatoren geladen waren, wurden die Ladungen durch Lichteinfall je nach Intensität verschieden schnell entladen. Nach einer gewissen (Belichtungs-)Zeit wurden die Zellen ausgelesen und dann in 1-Bit-Auflösung das Bild interpretiert. Für Graustufen musste man dasselbe Bild mehrfach mit verschiedenen Belichtungszeiten aufnehmen. Eine zusätzliche Verkomplizierung kam dadurch zustande, dass die Speicherzellen aus Gründen der Übersprechvermeidung nicht einfach nach ihren binären Adressen angeordnet sind, sondern diese Adressbits gezielt „verwürfelt“ werden. Daher mussten die Bilddaten nach dem Auslesen zunächst mit dem inversen Muster in die richtige Anordnung gebracht werden. Mit heutigen Chips geht das kaum noch, da sie normalerweise in Plastik-Vergussmasse eingebettet sind; außerdem sind Digitalkameras heute allgemein zugänglich und bezahlbar.

Bauarten

Es gibt eine Vielzahl von DRAM-Bauarten, die sich historisch entwickelt haben:

Derzeit sind eine Reihe von nichtflüchtigen RAM-Technologien (NVRAM) in der Entwicklung, wie:

Die Speicherkapazität wird in Bit und Byte angegeben.

Als Arbeitsspeicher verwendetes RAM wird häufig in Form von Speichermodulen eingesetzt:

Siehe auch

Literatur

Weblinks

Wikimedia Foundation.

![\begin{matrix} U & = & \frac{U_{BL}}{2} \cdot (1 \pm \frac{C}{C + C_{BL}}) \\[2ex]

& = & \underbrace{\frac{U_{BL}}{2}}_\mathrm{urspr\ddot{u}ngliche \atop Bitleitungsspannung} \pm \underbrace {\frac{U_{BL}}{2} \cdot \frac{C}{C + C_{BL}}}_\mathrm{Spannungs\ddot{a}nderung} \\

\end{matrix}](/pictures/dewiki/102/f269fee4465eef683141a567efa48354.png)