- Synchronzähler

-

Ein Synchronzähler ist ein Bauteil aus der Digitaltechnik, das eine Folge von natürlichen Zahlen erzeugt. Die Darstellung der Zahlen erfolgt im Dualsystem. Die Menge der darstellbaren Zahlen und ihre Reihenfolge ist bauteilabhängig. Die Anzahl der möglichen Zahlen ist auf Zweierpotenzen

![\left[0;\,2^n-1\right]](8/d38b90eba166d56699dc047d1d246816.png) festgelegt. Man spricht daher auch von n-bit-Synchronzählern.

festgelegt. Man spricht daher auch von n-bit-Synchronzählern.Inhaltsverzeichnis

Aufbau

Ein n-bit-Synchronzähler ist aus n JK-Flipflops aufgebaut. Der Takteingang jedes Flipflops ist mit einem Taktgeber CLK verbunden. Durch diese Struktur laufen alle Flipflops synchron zum externen Takt. Daher auch der Name des Bauteils (vgl. Asynchronzähler). Die Fähigkeit, eine Zahlenfolge zu erzeugen, ergibt sich durch die Verschaltung der Eingänge jedes einzelnen Flipflops.

Ein JK-Flipflop verhält sich wie ein T-Flipflop, wenn beide Eingänge denselben Pegel haben. Bei J = K = 1 wechselt der Pegel am Ausgang und bei J = K = 0 bleibt er unverändert. Diese Eigenschaft wird für den Synchronzähler verwendet. Im Folgenden wird ein 4-bit-Vorwärtszähler mit den Ausgängen Q0 bis Q3 beschrieben, der die Zahlen von 0000B (=0D) bis 1111B (=15D) in natürlicher Reihenfolge zählt.

Q3 Q2 Q1 Q0 Binärwert Dezimalwert 0 0 0 0 0000 0 0 0 0 1 0001 1 0 0 1 0 0010 2 0 0 1 1 0011 3 0 1 0 0 0100 4 0 1 0 1 0101 5 0 1 1 0 0110 6 0 1 1 1 0111 7 Q3 Q2 Q1 Q0 Binärwert Dezimalwert 1 0 0 0 1000 8 1 0 0 1 1001 9 1 0 1 0 1010 10 1 0 1 1 1011 11 1 1 0 0 1100 12 1 1 0 1 1101 13 1 1 1 0 1110 14 1 1 1 1 1111 15 Daraus ergibt sich folgende Verschaltung:

- Das am wenigsten signifikante Bit (Q0) soll bei jeder steigenden Taktflanke wechseln und wird daher direkt mit dem Taktgeber CLK verbunden.

- Das nächsthöhere Bit (Q1) soll nur wechseln, wenn der Ausgang Q0 den Pegel 1 hat (also während des vorigen Takts eine 1 ausgegeben hat). Dies wird realisiert, indem man Q0 mit den Eingängen des zweiten Flipflops verbindet

- Das nächsthöhere Bit (Q2) soll nur wechseln, wenn alle niedrigeren Bits (Q0 und Q1) den Pegel 1 haben (also während des vorigen Takt die Binärzahl 11 dargestellt haben). Dies wird mit einem UND-Gatter realisiert.

- Das nächsthöhere Bit (Q3) soll nur wechseln, wenn alle niedrigeren Bits (Q0, Q1 und Q2 ) den Pegel 1 haben (also im vorigen Takt die Binärzahl 111 dargestellt haben). Dies wird mit einem zusätzlichen Und-Gatter realisiert, welches das Ergebnis aus dem vorigen Schritt mitverwendet.

Das Beispiel lässt sich auf diese Weise fortsetzen um beliebig große Zähler zu erzeugen.

Eigenschaften

Da jedes Flipflop den externen Takt CLK bekommt, hat der Synchronzähler gegenüber dem Asynchronzähler den Vorteil, dass sich schaltzeitbedingte Verzögerungen nicht summieren und so höhere Taktraten und größere Zähler möglich sind. Ein weiterer Vorteil besteht darin, dass der Synchronzähler beliebige Zahlenfolgen darstellen kann (etwa 1, 3, 7, 5, …).

Varianten

Rückwärtszähler

Einen synchronen Rückwärtszähler erhält man, indem man in der oben beschriebenen Schaltung statt der Q-Ausgänge die

-Ausgänge verwendet. Mit jedem Takt zählt der Rückwärtszähler einen Schritt zurück. Wenn der untere Grenzwert 0 erreicht ist, springt der Rückwärtszähler beim nächsten Schritt wieder auf den Höchstwert.

-Ausgänge verwendet. Mit jedem Takt zählt der Rückwärtszähler einen Schritt zurück. Wenn der untere Grenzwert 0 erreicht ist, springt der Rückwärtszähler beim nächsten Schritt wieder auf den Höchstwert.Mit D-Flipflop

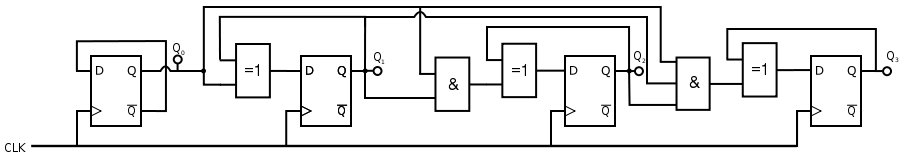

Die nachfolgende Schaltung zeigt einen Vorwärtszähler mit D-Flipflops. Sobald alle vorhergehenden Flipflops auf 1 geschaltet haben (Erkennung durch die UND-Gatter), wird der Eingang des nächsten Flipflops invertiert (durch Rückkopplung des eigenen Zustandes und einer XOR-Verknüpfung mit dem Ergebnis des UND-Gatters). Auch dieses Schema lässt sich beliebig fortsetzen um größere Zähler zu realisieren.

Um aus der nachfolgenden Logikschaltung einen Rückwärtszähler zu machen, müssen die inversen Flipflop-Ausgänge (

) verwendet werden, um den Zählerstand auszugeben. Die restliche kombinatorische Logik zur Ansteuerung der jeweils nachfolgenden Flipflops bleibt unverändert. Auch bei diesem Zähler ist dann

) verwendet werden, um den Zählerstand auszugeben. Die restliche kombinatorische Logik zur Ansteuerung der jeweils nachfolgenden Flipflops bleibt unverändert. Auch bei diesem Zähler ist dann  das niedrigste Bit (LSB).

das niedrigste Bit (LSB).Beliebige Zahlenfolgen

Für Zahlenfolgen, die nicht der natürlichen Reihenfolge entsprechen, müssen die oben beschriebenen UND-Gatter durch komplexere Schaltungen ersetzt werden. Mit Hilfe von Karnaugh-Veitch-Diagrammen kann man sich die Schaltung der eigenen Zählfolge erarbeiten. Hierzu nimmt man die Ausgänge des synchronen Zählers als Eingänge des KV-Diagramms und legt für jede Binärziffer ein einzelnes Diagramm an. Durch dieses Verfahren können alle Zählfolgen erstellt werden. Um die Schaltung zu minimieren, kann es möglich sein, dass ein Rückwärtszähler eine bessere Ausgangsbasis darstellt.

Beliebige Zahlenfolgen mit Wiederholungen

Sollen innerhalb einer Zählperiode eine oder mehrere Zahlen häufiger vorkommen (etwa 1,2,2,3) benötigt man einen Umcodierer. Zunächst weist man jeder Zahl der Folge eine neue Zahl zu, so dass die resultierende Folge keine doppelten Zahlen erhält. Im angegebenen Beispiel wäre das 1→0, 2→1, 2→2, 3→3. Aus der neuen Zahlenfolge (0,1,2,3) lässt sich wie gewohnt ein Synchronzähler erzeugen. Die Ausgänge werden nun mit Hilfe eines Umcodierers in die gewünschten Zahlenwerte transformiert.

Wikimedia Foundation.