- Flipflop

-

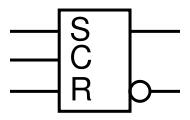

Schaltzeichen eines Flipflop nach DIN 40900 Teil 12

Schaltzeichen eines Flipflop nach DIN 40900 Teil 12

Ein Flipflop (engl. flip-flop), oft auch bistabile Kippstufe oder bistabiles Kippglied genannt, ist eine elektronische Schaltung, die zwei stabile Zustände einnehmen und damit eine Datenmenge von einem Bit über eine lange Zeit speichern kann. Es ist als Grundbaustein der sequentiellen Schaltungen ein unverzichtbares Bauelement der Digitaltechnik und damit fundamentaler Bestandteil vieler elektronischer Schaltungen von der Quarzuhr bis zum Mikroprozessor. Insbesondere ist es „massenhaft“ in bestimmten Ausführungen von Computerspeicherchips (statischen Speicherbausteinen) als elementarer 1 Bit-Speicher enthalten.

Inhaltsverzeichnis

Entstehung

Erfunden wurde die Flipflopschaltung 1918 von den Engländern William Henry Eccles und F. W. Jordan an rückgekoppelten Radioröhrenverstärkern auf der Suche nach Zählschaltungen,[1] und erhielt ursprünglich die Bezeichnung Eccles-Jordan-Schaltung.[2]

Charakteristik

Flipflops unterscheiden sich in der Anzahl und der logischen Funktion ihrer Eingänge (beschrieben durch ihre charakteristische Gleichung), der zeitlichen Reaktion auf diese Eingangssignale, insbesondere auf die Taktsignale (Timing), der Möglichkeit der direkten Rückführung von Ausgangssignalen auf die Eingänge (Transparenz oder Zähl-Flipflop) und dem strukturellen Aufbau (Master-Slave-Prinzip oder nicht). Gemeinsam ist jedoch allen, dass sie zwei stabile Zustände haben, welche an einem Ausgang gemessen werden können. Diese Zustände werden „gesetzt“ (set) und „zurückgesetzt“ (reset) genannt. Zwischen diesen Zuständen kann durch Signale an den Eingängen umgeschaltet werden. Üblicherweise ist neben dem Ausgang Q ein weiterer Ausgang Q vorhanden, an dem der negierte Wert von Q anliegt.

Wird ein Flipflop zum Beispiel in Transistor-Transistor-Logik (TTL) aufgebaut, dann entspricht der Zustand „gesetzt“ einer Spannung von 2,4 bis 5 Volt am Ausgang Q. An dem negierten Ausgang Q liegen dann 0 bis 0,4 Volt an. Bei der Verwendung von positiver Logik wird dieser Zustand als Q = 1 und Q = 0 interpretiert. In dem Zustand „zurückgesetzt“ liegen die Werte vertauscht an den Ausgängen an (Q = 0 und Q = 1).

Das einfachste Flipflop ist das ungetaktete RS-Flipflop, welches die zwei Eingänge S und R besitzt. Der Eingang S setzt den Ausgang des Flipflops, versetzt das Flipflop also in den Zustand „gesetzt“ (S = set). Der Eingang R setzt den Ausgang zurück, versetzt das Flipflop also in den Zustand „zurückgesetzt“ (R = reset). Die Eigenschaften des RS-Flipflops und anderer Flipflop-Arten werden weiter unten detaillierter erläutert.

Durch das Zusammenschalten mehrerer Flipflops entstehen komplexe Systeme wie Zähler (asynchron oder synchron), Datenspeicher (Halbleiterspeicher) und Mikroprozessoren. Flipflops sind Grundbausteine für die gesamte Digitaltechnik und Mikroelektronik von heute, einschließlich des Computers.

Klassifizierung anhand von Taktabhängigkeit

Nicht taktgesteuerte Flipflops

Der Zustand des oben eingeführten ungetakteten RS-Flipflop wird direkt durch die Pegel der Eingangssignale S oder R bestimmt. Solche Flipflops nennt man asynchrone pegelgesteuerte (level triggered) Flipflops. Es gibt aber auch die Möglichkeit, dass ein Flipflop seinen Zustand nur während eines Pegelwechsels der Eingangssignale ändert und der Pegel des Eingangssignals selbst keinen weiteren Einfluss hat. Solche Flipflops nennt man asynchrone flankengesteuerte (edge triggered) Flipflops. Zur praktischen Realisierung wurden früher Differenzierglieder verwendet. Heute werden die Flanken meist mit Hilfe von Laufzeitunterschieden in kurze Nadelimpulse verwandelt oder sie werden direkt durch flüchtige interne Zustände ausgewertet.

Taktgesteuerte Flipflops

Da die Eingangssignale nur in bestimmten Zeitabschnitten stabil anliegen, ist es oft gewünscht, dass ein Flipflop nur zu bestimmten Zeiten auf die Eingangssignale reagiert. Dieses Verhalten kann durch Verwendung eines Taktsignals realisiert werden, das die Steuereingänge des Flipflops zu bestimmten Zeiten freischaltet. Das Berücksichtigen eines Taktsignals ermöglicht auch Synchronität mit anderen Schaltungsteilen. Hier gilt es zu unterscheiden, auf welche Weise ein Flipflop Taktsignale berücksichtigt. Das folgende Bild zeigt diesbezüglich, wie verschiedene Flipflop-Typen voneinander abhängen.

Klassifizierung von Flipflops anhand ihrer Reaktion auf Taktsignale

Klassifizierung von Flipflops anhand ihrer Reaktion auf Taktsignale

Taktzustands- und taktflankengesteuerte Flipflops

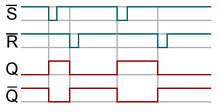

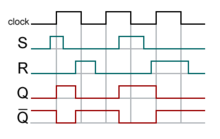

Impulsverläufe eines zustandsgesteuerten und eines vorderflankengesteuerten SR-Flipflops im Vergleich

Impulsverläufe eines zustandsgesteuerten und eines vorderflankengesteuerten SR-Flipflops im Vergleich

Taktgesteuerte Flipflops werden in synchronen Schaltwerken als Speicherelemente verwendet. Sie übernehmen ihre Daten- und Steuersignale durch ein (innerhalb des jeweiligen Schaltwerkes) einheitliches Taktsignal synchron und lassen sich in taktzustandsgesteuerte und taktflankengesteuerte Flipflops einteilen.

- Einfache taktzustandsgesteuerte Flipflops reagieren während der gesamten aktiven Taktphase auf die Eingangssignale und reichen deren Änderungen zum Ausgang durch. Solche transparenten taktpegelgesteuerten Bausteine sind nicht direkt rückkopplungsfähig und werden vor allem in der englischsprachigen Literatur als Latch, d. h. Klinkenschalter, bezeichnet (strenggenommen werden nur flankengesteuerte Bausteine als Flipflop bezeichnet).

- Übernimmt man den Zustand eines transparenten „Master-Flipflops“ mit der fallenden Taktflanke in ein „Slave-Flipflop“, dann entsteht ein rückkopplungsfähiges taktpegelgesteuertes „klassisches“ Master-Slave-Flipflop (z. B. Typ 7472), das als Zähl-Flipflop verwendet werden kann.

- Taktflankengesteuerte Flipflops können ihren Zustand nur während der Taktflanken ändern. Das Flipflop reagiert also nur während einer sehr kurzen Zeit nach der Taktflanke auf die Signale, die an den Eingängen anliegen. In der übrigen Zeit, zwischen den Flanken, bleibt der vorher eingestellte Zustand gespeichert und ändert sich, im Gegensatz zu taktzustandsgesteuerten Flipflops, auch dann nicht, wenn sich die Eingangssignale ändern. Damit sind taktflankengesteuerte Flipflops prinzipiell rückkopplungsfähig und können als Zähl-Flipflop verwendet werden. Man unterscheidet vorderflankengesteuerte (Wechsel bei steigender (positiver) Taktflanke), rückflankengesteuerte (Wechsel bei fallender (negativer) Taktflanke) und zweiflankengesteuerte (Übernahme mit steigender, Ausgabe mit fallender Taktflanke) Flipflops.

- Zweiflankengesteuerte Flipflops werden oft als „Master-Slave-Flipflop“ realisiert. Sie bestehen aus zwei hintereinandergeschalteten Flipflops. Die steigende Flanke setzt nur den vorderflankengesteuerten Master, die fallende übernimmt dessen Zustand in den Slave. Nur dieser ist nach außen geführt, so dass der Ausgang erst mit der fallenden Flanke reagiert. Da (echte) zweiflankengesteuerte Flipflops aber sehr aufwändig zu realisieren sind, werden sie praktisch selten eingesetzt.

Flipflop-Typen

Im Folgenden sind einige typische Flipflops dargestellt. Sie unterscheiden sich im Wesentlichen durch ihr logisches Verhalten, d.h. den Einfluss des aktuellen Zustandes und der Werte der aktuell anliegenden Eingangssignale (Daten- und Steuersignale) auf den Folgezustand. Dieser Einfluss wird durch die charakteristische Gleichung des Flipflops beschrieben. Diese beschreibt das äußere Verhalten des Flipflops und abstrahiert deshalb von der Art der Taktsteuerung. Sie wird meist in Form einer Wahrheitstabelle (auch Schaltfolge- oder Automatentabelle genannt) zur Spezifikation des Flipflops angeführt.

RS-Flipflop

Ein RS-Flipflop (Reset-Set-Flipflop) ist die einfachste Art eines Flipflops. Grundelement dieser Schaltungen ist ein Flipflop ohne Taktsteuerung, wie es in der nachfolgenden Tabelle in der ersten Zeile gezeigt ist. Mit geeigneter Zusatzbeschaltung können daraus sowohl taktpegelgesteuerte RS-Flipflops (asynchrone Schaltungen) als auch taktflankengesteuerte RS-Flipflops generiert werden. Diese RS-Flipflops dienen als Grundschaltungen zum Aufbau komplexerer Flipflops.

Ein RS-Flipflop verfügt über zwei Eingänge, die üblicherweise mit R (reset) und S (set) bezeichnet werden, ggf. ist ein dritter, typischerweise mit C (Clock) bezeichneter Eingang vorhanden, an den ein Taktsignal angelegt werden kann. Mit einem Signal am „Setz“-Eingang, das heißt S = 1 und gleichzeitig R = 0, wird der Ausgang Q des Flipflops auf 1 gesetzt. Aktiviert man hingegen den „Rücksetz“-Eingang (also R = 1 und gleichzeitig S = 0), so wird das Flipflop zurückgesetzt: Am Ausgang Q liegt dann eine logische 0 an. Liegt anschließend an beiden Eingängen eine 0 an, so verharrt das Flipflop in dem zuvor eingestellten Zustand. Besondere Aufmerksamkeit muss dem Eingangszustand gewidmet werden, bei dem sowohl R- als auch S-Eingang aktiv sind (R = S = 1 beim RS-Flipflop aus NOR-Gattern bzw.

beim RS-Flipflop aus NAND-Gattern). Dabei nimmt das zustandgesteuerte Flipflop einen dritten Zustand an, bei dem beide Ausgänge den Zustand 1 annehmen. Oft wird behauptet, dieser Zustand sei instabil, was allerdings nicht stimmt. Er ergibt nur einen logischen Widerspruch und wird deswegen auch „verbotener Zustand“ genannt. Ist das Flipflop taktgesteuert, können Änderungen der Ausgangszustände natürlich nur dann vorgenommen werden, wenn der steuernde Eingang aktiviert ist. Bei taktzustandsgesteuerten Flipflops muss dementsprechend eine 1 am Eingang C anliegen, bei Takt-Flankengesteuerten Flipflop eine geeignete Flanke (steigend oder fallend, je nach Konstruktion). Ein flankengesteuertes RS-Flipflop kann durch (annähernd) gleichzeitiges Takten beider Eingänge ebenfalls in einen undefinierten Zustand gelangen.

beim RS-Flipflop aus NAND-Gattern). Dabei nimmt das zustandgesteuerte Flipflop einen dritten Zustand an, bei dem beide Ausgänge den Zustand 1 annehmen. Oft wird behauptet, dieser Zustand sei instabil, was allerdings nicht stimmt. Er ergibt nur einen logischen Widerspruch und wird deswegen auch „verbotener Zustand“ genannt. Ist das Flipflop taktgesteuert, können Änderungen der Ausgangszustände natürlich nur dann vorgenommen werden, wenn der steuernde Eingang aktiviert ist. Bei taktzustandsgesteuerten Flipflops muss dementsprechend eine 1 am Eingang C anliegen, bei Takt-Flankengesteuerten Flipflop eine geeignete Flanke (steigend oder fallend, je nach Konstruktion). Ein flankengesteuertes RS-Flipflop kann durch (annähernd) gleichzeitiges Takten beider Eingänge ebenfalls in einen undefinierten Zustand gelangen.Ein Eingang kann jedoch dominierend geschaltet und somit der dritte Zustand vermieden werden. Solche Flipflops werden am dominierenden Eingang mit einer 1 nach dem Buchstaben gekennzeichnet. In der Automatisierungstechnik, beispielsweise bei speicherprogrammierbaren Steuerungen ist die Nutzung der Dominanz verpflichtend, da instabile oder nicht vorhersagbare Zustände hier nicht tolerierbar sind. Die Dominanz wird dabei dadurch sichergestellt, dass der dominante Zustand zeitlich nach dem dominierten programmiert wird und diesen somit überschreibt, so dass zum Synchronisationszeitpunkt das gewünschte dominierende Verhalten gewährleistet ist. Innerhalb von Multitaskingsystemen muss daher die Abarbeitung des Setzens und Rücksetzens gekapselt sein und darf nicht unterbrochen werden. Dominierende RS-Flipflops waren nicht als einzelne Hardwarebausteine erhältlich. Die Dominanz kam nur indirekt dann zum Einsatz, wenn ein komplexer Baustein mit Reset- und Set-Eingängen ausgestattet war. Als symbolisches Einzelelement traten sie erst in Erscheinung, als ihre Funktion durch Programmierung implementiert wurde.

Vergleich zwischen RS-Flipflop und WippeDie Arbeitsweise eines RS-Flipflops lässt sich grob mit der einer mechanischen Wippe vergleichen (dieser Vergleich motiviert auch die Bezeichnung Kippstufe). Eine Wippe besitzt zwei stabile Zustände: Einerseits, wenn ihr linkes Ende den Boden berührt, andererseits, wenn ihr rechtes Ende auf dem Boden aufliegt. Durch geeigneten Kraftaufwand kann man die Wippe von einem stabilen Zustand in den anderen stabilen Zustand überführen (bei einem Flipflop entspricht dies der Aktivierung der Eingänge, d. h. R = 0,S = 1 bzw. R = 1,S = 0). Lässt die steuernde Kraft nach (entspricht R = 0 und S = 0), so verharrt die Wippe in dem zuvor eingestellten Zustand: Dieser ist damit gleichsam gespeichert. Eine horizontale Ausrichtung der Wippe führt jedoch zu einem metastabilen Zustand (entspricht dem Fall R = 1 und S = 1): Da die Wippe nicht exakt symmetrisch gebaut ist und nicht alle äußeren Störeinflüsse ausgeschaltet werden können, kippt die Wippe nach einer bestimmten Zeit und nimmt einen der beiden stabilen Zustände ein, sobald die steuernde Kraft nachlässt. In der Regel kann nicht vorhergesagt werden, ob ihr linkes Ende oder ihr rechtes Ende in Richtung des Erdbodens kippen wird, da nicht alle Störungen exakt genug bekannt sind. Ein getaktetes Flipflop entspricht dabei einer Wippe, bei der die steuernde Kraft nur während einer durch ein äußeres Taktsignal bestimmten Zeit wirken kann.

In der folgenden Gegenüberstellung ist die erste Ausführung mit negierten Signalnamen am Eingang ausgeführt. Das heißt, dass der Ruhezustand der Eingangssignale durch den 1-Pegel gebildet wird, und der aktive, schaltende Zustand durch 0-Pegel der Eingänge. Das ist durch den Aufbau des Flipflops aus NAND-Gattern bedingt und durchaus auch in der Praxis üblich. Bei der zweiten Ausführung ist den Eingängen praktisch eine zusätzliche Inverterstufe vorgeschaltet, so dass hier wieder mit „echten“ Signalnamen gearbeitet wird.

Name Schaltsymbol Impulsdiagramm Ersatzschaltbild Wahrheitstabelle Asynchrones RS-Flipflop

Impulsdiagramm mit negierten Signalnamen am Eingang Logik-Schaltung eines RS-Flipflops aus zwei NAND-Gattern (ungetaktet) Die Eingänge des Flipflops besitzen die negierten Signalnamen R und S, da diese ihre (aktive) Rücksetz- bzw. Setz-Funktion mit 0 ausführen.

S R Q 1 1 unverändert 0 1 1 (gesetzt) 1 0 0 (zurückgesetzt) 0 0 Q=Q=1 (wird nicht gespeichert; potenzielle Race condition) RS-Flipflop mit Taktpegelsteuerung (taktpegelgesteuert) S R C Q 0 0 0 unverändert 0 0 1 unverändert 0 1 0 unverändert 0 1 1 0 (zurückgesetzt) 1 0 0 unverändert 1 0 1 1 (gesetzt) 1 1 0 unverändert 1 1 1 Q=Q=1 (wird nicht gespeichert; potenzielle Race condition) JK-Flipflop

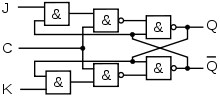

Eine weitere Klasse von Flipflops, die primär in diskreten digitalen Schaltungen Anwendung findet, sind die JK-Flipflops. Sie wurden wahrscheinlich nach Jack Kilby benannt, werden aber oft Jump-/Kill-Flipflops genannt, da bei der Eingangsbeschaltung J = 1 eine 1 und bei K = 1 eine 0 gespeichert wird. Sie sind fast immer als flankengesteuertes Bauelement ausgeführt. Der Eingang C kann für steigende Flanken (Wechsel von 0 auf 1) oder für fallende Flanken (Wechsel von 1 auf 0) ausgelegt werden. Der Zustand J = K = 1 ist erlaubt. In diesem Fall wechselt der Ausgangspegel mit jeder wirksamen Flanke des Taktsignals, was dem Verhalten eines Toggle-Flipflops entspricht. Für J = K = 0 bleibt der Zustand erhalten.

Bei JK-Flipflops muss als wesentliche Einschränkung beachtet werden, dass sich bei aktivem Taktzustand (C = 1) die Zustände der beiden Eingänge J und K nicht mehr ändern dürfen. Es liegt also kein rein taktflankengesteuertes Flipflop vor. Dieser Nachteil ist auch der primäre Grund, warum JK-Flipflops in komplexen Digitalschaltungen nur noch selten verwendet werden und primär durch einflankengetriggerte D-Flipflops ersetzt werden, die diesen Nachteil nicht aufweisen.

Name Schaltsymbol Impulsdiagramm Ersatzschaltbild Wahrheitstabelle JK-Flipflop

während des Taktes nach Taktflanke J K Q 0 0 unverändert 0 1 0 (Flipflop zurückgesetzt) 1 0 1 (Flipflop gesetzt) 1 1 Zustand wechselt (toggle) Viele der erhältlichen Flipflops vereinen verschiedene Bauformen in sich und sind so vielseitiger einsetzbar.

D-Flipflop

Taktflanken-gesteuertes D-Flipflop

Taktflanken-gesteuertes D-Flipflop

D-Flipflops (Data-Flipflops, oft auch bezeichnet als Delay-Flipflops zum Verzögern des Datensignals um einen Takt) erschienen als Einzelbausteine erstmals in den 1960er Jahren. Diese besitzen einen Daten- (D) und einen Clock-Eingang (C, oft dargestellt als „>“). Oft ist noch ein sogenannter Clock-Enable-Eingang (CE) vorhanden, mit dem der Takteingang in seiner Funktion freigeschaltet werden kann (engl. enable = freigeben). Als Ausgang kommt Q und nur selten der dazu invertierte Ausgang vor. Aus diesem elementaren Flipflop lassen sich durch externe Beschaltung alle weiteren taktflankengesteuerten Typen von Flipflops und komplexere Schaltungen wie Synchronzähler, Taktteiler oder auch Schieberegister realisieren.

Das D-Flipflop speichert bei freigeschaltetem Takteingang und aktiver Taktflanke den logischen Zustand des Eingangs und gibt seinen Wert in Folge auf Q aus. Liegt keine aktive Taktflanke an oder ist der Clock-Enable-Eingang deaktiviert, erfolgt keine Übernahme des Eingangswertes.

Davon zu unterscheiden ist das taktzustandsgesteuerte D-Flipflop, auch als D-Latch bezeichnet, welches aus einem RS-Flipflop erweitert um einen Taktzustandseingang besteht. Diese Gruppe wird insbesondere in der englischsprachigen Literatur und zur Unterscheidung von dem taktflankengesteuerten D-Flipflop als Latch bezeichnet. Solange der Takteingang C aktiv ist, nimmt das Latch den Zustand an, der am Eingang D anliegt, das ist der transparente Zustand. Der Vorteil des D-Latch ist, dass der illegale Zustand R = S = 1 vermieden wird. Der Nachteil besteht darin, dass es wie alle taktzustandsgesteuerten Flipflops einen direkten Durchgriff des Eingangs D auf den Ausgang Q aufweist und damit insbesondere in synchronen digitalen Schaltungen, wie in FPGAs, unbestimmte Zeitverhältnisse auftreten können.

Wegen ihrer eingängigen Funktionsweise haben sich D-Flipflops bis heute als verbreitetes Beschreibungssymbol für Einzelfunktionen in hochintegrierten Bausteinen wie Microcontrollern, Field Programmable Gate Array (FPGAs) und ASICs erhalten.

T-Flipflop

Ein asynchrones T-Flipflop (Toggle-Flipflop) wechselt mit jedem Taktimpuls seinen Ausgangszustand. Seine erste Realisierung in elektromechanischer Bausteinform wurde schon im 19. Jahrhundert als Treppenhausschalter prominent und ist heute noch bei Neuinstallationen verbreitet im Einsatz. Das asynchrone T-Flipflop kann durch ein (synchrones) D-Flipflop gebildet werden, wenn dessen Ausgang Q invertiert auf den Eingang D zurückgeführt wird. T steht dabei für englisch toggle – Hin- und herschalten. Vor allem bei diskreten Digitalschaltungen wird zur Realisierung eines asynchronen T-Flipflops manchmal auch das oben beschriebene JK-Flipflop verwendet. Dabei müssen beide Eingänge des JK-FF auf logisch »1« gelegt werden.

Ein asynchrones T-Flipflop funktioniert ähnlich wie ein Druckkugelschreiber oder ein Stromstoßrelais (Stromstoßschalter). Wegen der oben schon erwähnten Eigenschaft des mit halber Frequenz des Taktsignals wechselnden Ausgangspegels dienen diese Flipflops vor allem als Frequenzteiler und als Grundelement in asynchronen digitalen Zählern. Man verwendet sie auch, um ein Rechtecksignal mit einem Tastverhältnis von exakt 1:1 zu gewinnen.

bgc Q 0 0 1 1 0 1 1 0 Demgegenüber besitzt das synchrone T-Flipflop (neben dem Takteingang C) einen T-Eingang. Nur wenn an diesem eine 1 anliegt, schaltet das synchrone T-Flipflop mit dem Takt in den anderen Zustand. Es kann z. B. aus einem JK-Flipflop nachgebildet werden, indem J-Eingang und K-Eingang zum T-Eingang verbunden werden. Das synchrone T-Flipflop wird beispielsweise in Synchronzählern verwendet.

Zusätzliche asynchrone Steuereingänge bei Flipflops

Je nach Bauart besitzen die getakteten Flipflops (taktzustandsgesteuerte oder taktflankengesteuerte Flipflops) auch noch zusätzliche asynchrone Steuereingänge. Die asynchronen Steuereingänge beeinflussen das Flipflop auch ohne Taktsignal. Je nach Bauart besitzen diese Bauelemente einen zusätzlichen asynchronen Reset-Eingang, einen asynchronen Set-Eingang oder beide Eingänge zusammen. Das asynchrone Reset wird manchmal auch als „Clear“ (=Löschen) bezeichnet, während das asynchrone Setzen auch als 'Preset' (=Vorbelegen) bezeichnet wird.

Durch einen asynchronen Reset-Eingang kann das Flipflop unabhängig vom Takt in den definierten Anfangszustand (Ausgang = 0) gebracht werden. Diese Funktion beim Bauelement wird beispielsweise als asynchroner Reset beim Einschalten der Versorgungsspannung verwendet oder wenn die Schaltung während des Betriebs wieder in einen definierten Zustand (Reset-Zustand) gebracht werden muss. Der asynchrone Set-Eingang verhält sich analog wie der asynchrone Reset-Eingang, bringt aber das Flipflop in den Setz-Zustand (Ausgang = 1). Eine gleichzeitige Betätigung des asynchronen Setz- und Rücksetzeingangs zusammen kann das Flipflop je nach Bauart aber in einen undefinierten Zustand bringen. Häufig werden die beiden zusätzlichen asynchronen Eingänge low-aktiv angesteuert. Das asynchrone Reset-Signal kann dann direkt an einen Reset-Generator mit einem Low-aktiven Schaltausgang angeschlossen werden.

Timing der Flipflops

Bei der ingenieurmäßigen Anwendung der Flipflop-Bauelemente bei Elektronik-Schaltungen müssen verschiedene Zeitbedingungen beachtet werden. Betrachten wir beispielsweise ein taktflankengetriggerten D-Flipflop mit Einflankentriggerung. Als Referenz für jeden einzelnen Schaltvorgang betrachten wir beim Flipflop die aktive Schaltflanke des Takts (clk). Das Eingangssignal (D-Eingang) des Flipflops darf sich vor der aktiven Schaltflanke des Taktsignals für eine definierte Mindestdauer nicht ändern. Diese Zeit wird als Setup-Zeit tSU (engl. setup-time) bezeichnet.

Weiterhin darf sich der Logikzustand am D-Eingang nach der aktiven Schaltflanke des Taktsignals für eine definierte Mindestdauer ebenfalls nicht ändern. Diese Zeit wird als Haltezeit tH (engl. hold-time) bezeichnet. Weiterhin gibt es bei den Flipflops noch die Signallaufzeit durch das Bauelement (engl. propagation delay time) tPD (siehe auch Laufzeittoleranzrechnung).

Die maximale Taktfrequenz des Taktsignals fclk,max darf nicht überschritten werden. Als weitere Timingvorgabe beim Taktsignal tritt beim Flipflop die Pulsbreite des Taktsignals tPW,clk (engl. pulse-width) auf. Diese Mindestlänge des Taktsignals (beginnt ab der aktiven Taktflanke und endet bei der umgekehrten Taktflanke des Impulses) darf nicht unterschritten werden, damit das Flipflop sicher schalten kann.

Bei Flipflops mit zusätzlichen asynchronen Steuereingängen darf es bei den asynchronen Steuereingänge ebenfalls für eine definierte Mindestzeit vor der aktiven Taktflanke beim Taktsignals CLK keine Signaländerung geben. Weiterhin dürfen sich die asynchronen Steuereingänge nach der aktiven Taktflanke für eine definierte Mindestdauer nicht ändern.

Wenn die Timing-Vorgaben beim Flipflop nicht eingehalten werden, kann davon ausgegangen werden, dass es zu Fehlfunktionen bei den Flipflops kommt.

Im Beispiel ist das Timing beim D-Flipflop beschrieben. Alle anderen Flipflops mit Takteingang, z. B. beim T-FF, haben grundsätzlich das gleiche Verhalten. Beim RS-Flipflop und JK-Flipflop muss analog zum D-Flipflop ebenfalls die Setup-Time tSU und die Hold-Time tH eingehalten werden. Da diese beiden Flipflop-Typen jeweils 2 Eingänge besitzen gilt die Zeitvorgabe dann jeweils für den R- und S-Eingang bzw. J- und K-Eingang.

Schaltzeichen verschiedener Flipflop-Typen

Verwendung von Flipflops

Einfaches Beispiel einer Aufzugsteuerung

An dem einfachen Beispiel einer Aufzugsteuerung soll die Speicherfunktion eines SR-Flipflops verdeutlicht werden. Wir betrachten einen Aufzug in einem mehrgeschossigen Gebäude. Auf jeder Etage befindet sich ein Rufknopf für den Aufzug. Der Vorgang ist aus dem Alltag bekannt: Drückt man die Ruftaste, so leuchtet diese auch dann noch auf, wenn man den Knopf loslässt. Der Rufbefehl bleibt also gespeichert, auch wenn der Schalter nicht gedrückt bleibt. Das Licht hinter der Taste verlischt erst, wenn der Aufzug auf unserer Etage angehalten und die Türen geöffnet hat. Erst jetzt ist auch der Rufbefehl gelöscht. Ein solches Verhalten lässt sich mit einem SR-Flipflop realisieren. Dazu benötigen wir für jede Etage einen Flipflop. Seine beiden Eingänge (S und R) legen wir dazu jeweils an eine Spannungsquelle (HI = High), die eine für eine logische 1 hinreichend große Spannung liefert. Zwischen Spannungsquelle und den Flipflop-Eingängen sitzen jeweils Taster. Der eine Taster ist mit dem Rufknopf der jeweiligen Etage verbunden, der andere Taster kann nur vom Aufzug selbst bedient werden. Indem wir die Ruftaste auf einer Etage drücken, schließen wir kurz die Verbindung zwischen der Spannungsquelle und dem S-Eingang des Flipflops, der für unsere Etage zuständig ist. Damit wird wegen S=1 und R=0 der Flipflop gesetzt:

und Q = 0. Der Ausgang Q speichert damit den Rufbefehl. Lassen wir den Knopf wieder los, schnellt der Taster zurück, die Verbindung zwischen der Spannungsquelle und dem Eingang S ist unterbrochen, der Eingang S des Flipflops fällt auf 0 zurück (S = 0 und R=0). Dennoch verharrt das Flipflop in dem zuvor eingestellten Zustand: Q bleibt nämlich solange auf 1, bis der Reset-Eingang aktiviert wird (Speicherfall). Der Aufzug setzt sich nun in Bewegung. Sobald er an unserer Etage anhält und seine Türen öffnet, betätigt ein Mechanismus den Taster, der den R-Eingang und die Spannungsquelle verbindet. Dadurch wird wegen S = 0 und R=1 der Rufbefehl gelöscht (Q = 0) und bleibt solange gelöscht, bis ein weiterer Besucher die Ruftaste erneut drückt. In der Realität ist die Steuerung natürlich weit komplexer, die in den jeweiligen Etagen gespeicherten Rufbefehle werden an eine Steuerelektronik des Aufzugs gegeben, die dann aus diesen und aus den in der Aufzugkabine gedrückten Tasten eine sinnvolle Reihenfolge errechnet, nach der die Etagen angefahren werden sollen.

und Q = 0. Der Ausgang Q speichert damit den Rufbefehl. Lassen wir den Knopf wieder los, schnellt der Taster zurück, die Verbindung zwischen der Spannungsquelle und dem Eingang S ist unterbrochen, der Eingang S des Flipflops fällt auf 0 zurück (S = 0 und R=0). Dennoch verharrt das Flipflop in dem zuvor eingestellten Zustand: Q bleibt nämlich solange auf 1, bis der Reset-Eingang aktiviert wird (Speicherfall). Der Aufzug setzt sich nun in Bewegung. Sobald er an unserer Etage anhält und seine Türen öffnet, betätigt ein Mechanismus den Taster, der den R-Eingang und die Spannungsquelle verbindet. Dadurch wird wegen S = 0 und R=1 der Rufbefehl gelöscht (Q = 0) und bleibt solange gelöscht, bis ein weiterer Besucher die Ruftaste erneut drückt. In der Realität ist die Steuerung natürlich weit komplexer, die in den jeweiligen Etagen gespeicherten Rufbefehle werden an eine Steuerelektronik des Aufzugs gegeben, die dann aus diesen und aus den in der Aufzugkabine gedrückten Tasten eine sinnvolle Reihenfolge errechnet, nach der die Etagen angefahren werden sollen.Breite Verwendung in der Digitalelektronik

Flipflops können als 1-Bit-Speicher betrachtet werden. Aus ihnen können Register verschiedener Wortbreiten zusammengesetzt werden, wie sie beispielsweise in Mikroprozessoren Verwendung finden.

Auch die einzelnen Speicherzellen von statischen RAMs bestehen aus Flipflop-Schaltungen. Beim dynamischen RAM hingegen besteht eine Speicherzelle nur aus einem Kondensator und einem Transistor.

Weiterhin sind Flipflops unverzichtbar in digitalen Zählschaltungen. Hier kommen besonders D- oder T-Flipflops (verschiedener Typen) als Frequenzteiler zum Einsatz.

In Quarzuhren teilt eine Kette von 15 Flipflops die Oszillatorfrequenz 32768 Hz durch 215 und liefert Sekundenimpulse.

Bei den oben beschriebenen Anwendungen sind die Flipflops typischerweise Teil eines größeren Elektronikbauelements. In der ingenieurmäßigen Schaltungsentwicklung werden Flipflops heute kaum mehr als Einzelbauelemente eingesetzt. Heute werden typischerweise Bauelemente eingesetzt, die neben Flipflops auch weitere Schaltungsfunktionen in einem gemeinsamen Bauelement beinhalten. Hierunter fallen unter anderem auch die FPGA-, PLD- und ASIC-Bauelemente. In diesen Bauelementen sind typischerweise D-Flipflops enthalten.

Weblinks

Commons: Flip-flops – Sammlung von Bildern, Videos und Audiodateien

Commons: Flip-flops – Sammlung von Bildern, Videos und Audiodateien- Flipflops interaktiv (Java erforderlich)

- Interaktive Simulation von verschiedenen Flipflop-Typen mit dem Hades simulation framework (englisch)

- Interaktive LogiFlash-Animationen (Rubrik „2 Speicherglieder“)

- Weitere Informationen über Kippglieder und Zählwerke

- Mehr Informationen zu RS- und JK-Flipflops (Homepage deutsch/englisch)

Literatur

- Manfred Seifart, Helmut Beikirch: Digitale Schaltungen. Verlag Technik, Berlin 1998, ISBN 3-341-01198-6.

- Gerd Scarbata: Synthese und Analyse Digitaler Schaltungen. Oldenbourg Wissenschaftsverlag GmbH, München 2001, ISBN 3-486-25814-1.

Einzelnachweise

- ↑ Radio Review. Dez. 1919, S. 143 ff

- ↑ Zur Geschichte: Robert Dennhardt: Die Flipflop-Legende und das Digitale : eine Vorgeschichte des Digitalcomputers vom Unterbrecherkontakt zur Röhrenelektronik 1837 - 1945. Kulturverlag Kadmos, Berlin 2009, Zugleich: Diss. Humboldt-Universität,, Berlin 2007, ISBN 978-3-86599-074-7.

Wikimedia Foundation.