- Floating-Gate-Transistor

-

Ein Floating-Gate-Transistor ist ein spezieller Transistor, der in nichtflüchtigen Speichern zur permanenten Informationspeicherung eingesetzt wird. Er wurde 1967 von Dawon Kahng und S.M. Sze in den Bell Laboratories entwickelt [1] und stellt in integrierten Schaltungen bei den heute üblichen Flash-Speichern, EPROMs und EEPROMs das elementare Speicherelement dar.

Allgemeines

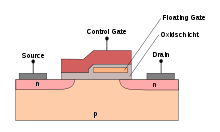

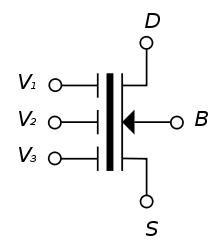

Floating-Gate-Transistoren, abgekürzt auch als FGMOS bezeichnet, zählen zu der Gruppe der Feldeffekttransistoren mit isoliertem Gate (IGFETs) und werden aus dem Halbleitermaterial Silicium hergestellt. Er besteht aus einem oder mehreren „Floating-Gates“ (Bezeichnung V, dt. ‚nicht geerdete Steuerelektrode‘), die elektrisch isoliert sind. Diese Floating-Gates können eine bestimmte Menge an elektrischer Ladung permanent speichern. Zum Beschreiben bzw. Auslesen der Information dienen die Anschlüsse Source (S) und Drain (D), die eine ähnliche Funktion wie bei herkömmlichen IGFETs aufweisen. Der Anschluss Bulk (B) ist meist mit Massepotential verbunden.

Das Einbringen bzw. Entfernen der elektrischen Ladung im Rahmen des Schreibvorganges auf das elektrisch durch Siliciumdioxid isolierte Floating-Gate erfolgt durch den quantenmechanischen Tunneleffekt bzw. durch Feldemission (engl. hot carrier injection) vom Source- bzw. Drain-Anschluss aus, unter Zuhilfenahme eines Steueranschlusses (engl. control gate). Für den Programmiervorgang ist eine elektrische Spannung im Bereich von 10 V notwendig. Für den Auslesevorgang hingegen ist nur die normale Betriebsspannung, üblich sind Spannungen um 3,3 V, ausreichend.

Durch die am Floating-Gate eingebrachte Ladung verbleibt die Drain-Source-Strecke des Transistors in einem niederohmigen Zustand. Bei fehlender Ladung am Floating-Gate ist die Drain-Source-Strecke hingegen hochohmig. Mit diesen beiden Zuständen kann im einfachsten Fall die Informationsmenge von einem Bit permanent gespeichert werden. Je nach konkreter Speichertechnologie umfasst der Transistor wie bei der SLC-Speicherzelle ein Floating-Gate oder mehrere Floating-Gates, wie sie bei MLC-Speicherzellen anzutreffen sind. Bei MLC-Speicherzellen können in einem Transistor durch Abstufungen der Ladungsmengen mehr als ein Bit an Information gespeichert werden, was die Speicherdichte steigert. Übliche Werte sind zwei Bit pro Floating-Gate-Transistor mit vier verschiedenen Ladungsniveaus.

Zustandstabelle eines Floating-Gate-Transistors [2] Vorgang Gatespannung Sourcespannung FG-Ladung Schwellspannung Transistor Drainspannung logischer Pegel Lesen 3,3 V GND ungeladen normal leitet low (GND) 0 Lesen 3,3 V GND negativ geladen erhöht sperrt high 1 Schreiben > 10 V GND ladend steigt > 10 V 0 auf 1 Löschen GND GND entladend fällt > 10 V auf 0 Anwendungen

Der primäre Anwendungsbereich dieser Transistoren liegt im Bereich digitaler, nicht flüchtiger Speicher wie beispielsweise USB-Massenspeichern oder SD-Speicherkarten. Bei einer Speicherkapazität von 4 GB sind 35 Milliarden Floating-Gate-Transistoren notwendig.

Im Jahr 1989 entwickelte die Firma Intel im Rahmen einer Forschungsarbeit eine nicht flüchtige Speicherzelle (ETANN) basierend auf FGMOS für die Speicherung von analogen Größen im Rahmen von neuronalen Netzen.[3]

Einzelnachweise

- ↑ D. Kahng, S. M. Sze: A floating-gate and its application to memory devices. In: The Bell System Technical Journal. 46, Nr. 4, 1967, S. 1288–1295.

- ↑ A. Kolodny, S. T. K, Nieh, B. Eitan, J. Shappir: Analysis and modeling of floating-gate EEPROM cells. In: IEEE Transactions on Electron Devices. 33, Nr. 6, 1986, S. 835–844, doi:10.1109/T-ED.1986.22576.

- ↑ M. Holler, S. Tam, H. Castro, R. Benson: An electrically trainable artificial neural network with 10240 ‚floating gate‘ synapses. In: Proceeding of the International Joint Conference on Neural Networks, Washington, D.C. Volumen II, 1989, S. 191–196.

Wikimedia Foundation.