- High-k+Metal-Gate-Technik

-

Die High-k+Metal-Gate-Technik (HKMG-Technik) bezeichnet in der Halbleitertechnik einen speziellen Aufbau von Metall-Isolator-Halbleiter-Feldeffekttransistoren (MISFETs) von modernen integrierten Schaltkreisen (IC). Die Technik ist charakterisiert durch den Einsatz von Materialien mit einer höheren relativen Permittivität als Siliciumdioxid, sogenannte High-k-Materialien, als Isolationsschicht und einer Gate-Elektrode aus Metall (metal gate).

Inhaltsverzeichnis

Hintergrund

Die stetige Skalierung von mikroelektronischen Bauelementen seit Ende der 1970er Jahre führte dazu, dass die Strukturbreite – Abstand zwischen zwei Kontaktlöchern für den Anschluss von – von ICs von mehreren Mikrometern auf nur noch 90 nm im Jahr 2003 verkleinert wurde. Die Skalierung war notwendig, um die Integrationsdichte (Anzahl von Bauelementen pro Fläche) von ICs zu erhöhen.

Mitte der 2000er Jahre stieß diese Skalierung an ihre Grenzen. Denn mit der Skalierung der Strukturbreite ist auch eine Skalierung aller anderen Komponenten des MISFETs verbunden. So wurde seit den 1960er Jahren vorrangig amorphes Siliciumdioxid, das durch thermische Oxidation des Siliciumsubstrats hergestellt wurde, als Isolationsschicht zwischen dem halbleitenden Kanalgebiet und der Gate-Elektrode eingesetzt. Die Dicke der Isolationsschicht betrug in den 2000er Jahren nur noch wenige Atomlagen (ca. 1–2 nm). Bei diesen Schichtdicken nimmt der Einfluss von Tunneleffekten und minimalen Fertigungstoleranzen deutlich zu, so dass auftretende Tunnelströme durch die Isolationsschicht einen bedeutenden Anteil an der Verlustleistung der ICs hatten.

Da die Dicke aus den oben genannten Gründen bei dem 2005 von Intel eingeführten 65-nm-Fertigungsprozess nicht weiter reduziert werden, wurde schon zuvor nach alternativen Materialien für die Isolationsschicht aus Siliciumdioxid (SiO2) gesucht. Die Lösung lag in der Einführung sogenannter High-k-Dielektrika, die bei gleichen elektrischen Eigenschaften (wichtig ist hier vor allem die elektrische Kapazität des MISFETs) höhere Schichtdicken und somit geringe Tunnelströme ermöglichen (vgl. Gründe für den Einsatz von High-k-Dielektrika).

Bei der Erprobung von elektrischen Bauelementen mit High-k-Dielektrika und einen Polysilicium-Gate sind weitere negativ wirkende Effekte aufgetreten. Dazu zählen vor allem eine Erhöhung der Schwellspannung gegenüber theoretischen Annahmen und eine verringerte Ladungsträgerbeweglichkeit. Das sogenannte Fermi-level pinning verursacht, dass die realen Schwellspannungen höher liegen, als sie durch die Dotierung des Kanalgebiets und die Dicke der Isolationsschicht theoretisch sein sollten. Dieser Effekt wird durch die Anpassung der Austrittsarbeit mithilfe zusätzlicher Metallschichten an der Grenzfläche von der Gate-Elektrode zum High-k-Material kompensiert. Jeder Transistortyp (p-Kanal- und n-Kanal-Transistoren) benötigt jedoch eine eigene Anpassung, was die Komplexität nochmals erhöht. Dies betrifft vor allem den Einsatz von Bulk-Silicium-Substraten, bei Silicon-on-Insulator-Substrate ist diese Problematik weniger stark ausgeprägt.[1] Problematisch ist auch der Umstand, dass die Austrittsarbeit des Metalls möglichst dem von hoch dotiertem Silicium entsprechen sollte. Umfangreiche Studien zeigten jedoch, dass kein exakt passendes Metall existiert und man die Austrittsarbeit von Metallen anpassen muss, beispielsweise durch Dotierung.

Weiterhin wurde bei Transistoren eine verringerte Ladungsträgerbeweglichkeit (low charge-carrier mobility) beobachtet. Verursacht wird dies durch die schwingenden Dipole im High-k-Material, die zu Schwingungen im Kristallgitter des Halbleiters führen (sogenannte Phononen). Die Phononen wiederum streuen die Ladungsträger im grenzflächennahen Bereich des Kanalgebiets und verlangsamen diese. Die Folge ist eine verringerte Schaltgeschwindigkeit des Transistors. Wie sich herausstellte, beeinflusst die Ladungsträgerdichte in der Gate-Elektrode (an der Grenzfläche zum Dielektrikum) diesen Effekt. Da Metalle eine um mindestens zwei Größenordnungen höhere Ladungsträgerdichte aufweisen als Silicium, stellt der Einsatz eines metallischen Gates eine deutliche Verbesserung dar.[2]

Mit der Einführung der HKMG-Technologie beim 45-nm-Technologieknoten im Jahr 2007, war Intel das erste Unternehmen, das die HKMG-Technik in kommerziellen Produkten einsetzte. Als High-k-Material diente damals ein Hafniumoxid basiertes Material und die Herstellung erfolgte in dem sogenannten Gate-Last-Prinzip (siehe unten). Mit der Wiedereinführung einer metallischen Gate-Elektrode wurde der Effekt der Ladungsträgerverarmung innerhalb des Polysilicium-Gates umgangen. Er stellte eine zunehmende Herausforderung bei der IC-Fertigung dar. Damit wurde aus dem seit Mitte der 1980er Jahre Polysilicium-Siliciumdioxid-Feldeffekttransistor, der streng genommen kein MISFET bzw. MOSFET mehr war, wieder ein Metall-Oxid-Halbleiter-Feldeffekttransistor (MOSFET). Insgesamt führte der Einsatz von HKMG zur Einführung zahlreicher neuer Materialien und chemischer Stoffe im Fertigungsprozess.

Herstellungstechniken

Der Begriff HKMG beschreibt nur den nach der Fertigung vorliegenden Schichtstapel und macht keine Aussagen über die eingesetzten Materialien. Weiterhin erlaubt der komplexe Aufbau des Transistors Variationen hinsichtlich der eingesetzten Fertigungsprozesse und deren Reihenfolge. Die HKMG-Technik unterteilt sich daher nochmal in drei wesentliche Herstellungsstrategien:

- gate first; auch metal inserted poly-silicon, MIPS, genannt)

- gate last; auch replacement metal gate, RMG, replacement gate, RG, oder damascene gate, genannt)

- fully silicided gate (FUSI, dt. ‚vollkommen siliciertes Gate‘)

Dabei bezieht sich das first (engl. für ‚zuerst‘) und last (engl. für ‚zuletzt‘) darauf, ob die metallische Gate-Elektrode vor (first) oder nach (last) der Aktivierung der Source- und Drain-Gebiete hergestellt wird. Bei der Aktivierung handelt es sich um einen Hochtemperaturprozess, der die durch Ionenimplantation eingebrachten Dotierungsatome in das Kristallgitter integrieren soll.

Gate-First-Prozess

Beim Gate-First-Prozess wird die metallische Gate-Elektrode vor der Implantation und Aktivierung der Source- und Drain-Gebiete hergestellt. Das umfasst die Abscheidung des High-k-Dielektrikums und des Gate-Elektrode (ggf. mit den zusätzlichen Schichten für die Anpassung der Austrittsarbeit). Abschließend wird meist noch eine Opferschicht aus Polysilicum aufgebracht, dass den Gate-Stapel vor der nachfolgenden Implantation der Source- und Drain-Gebiete schützt.

Der wesentliche Vorteil des Gate-First-Ansatzes ist, dass die Prozessreihenfolge im Wesentlichen der eines Polysilicium-Gates entspricht, das heißt, es sind weniger Anpassungen an den Herstellungsprozess notwendig.

Gate-Last-Prozess

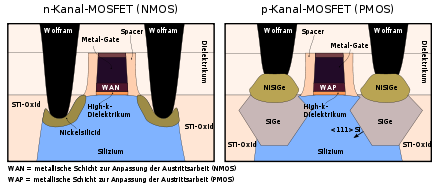

Schematische Querschnitte durch ein n-Kanal und ein p-Kanal-MOSFET in High-k+-Metal-Gate-Technik (in Replacement-Metal-Gate-Technik) wie ihn Intel 2007 mit den Penryn-Prozessoren in 45-nm-Technik einführte.

Schematische Querschnitte durch ein n-Kanal und ein p-Kanal-MOSFET in High-k+-Metal-Gate-Technik (in Replacement-Metal-Gate-Technik) wie ihn Intel 2007 mit den Penryn-Prozessoren in 45-nm-Technik einführte.

Beim Gate-Last-Prozess wird die metallische Gate-Elektrode erst nach der Implantation und Aktivierung der Source- und Drain-Gebiete hergestellt. Optional kann auch die High-k-Schicht erst nach der Implantation erfolgen.

Das gängigste Verfahren dafür ist die sogenannte Replacement-Metal-Gate-Technik (RMG) Hierzu wird zunächst ein konventionelles Polysilicium-Gates hergestellt und die Implantation/Aktivierung der Source- und Drain-Gebiete durchgeführt. Nun wird das Polysilicium der Gate-Elektrode selektiv entfernt, quasi eine Opferschicht (im englischen häufig Dummy-Gate genannt). Wurde zunächst noch kein High-k-Material als Dielektrikum abgeschieden wird auch dieses selektiv geätzt. Anschließend wird das nun „leere“ Gate mit dem gewünschten Schichtstapel (High-k-Dielektrika, Anpassungsmetalle und Gate-Elektrode) gefüllt.

Der Vorteil des Gate-Last-Ansatzes ist die geringere thermische Belastung des High-k-Materials und der Metallschichten, denn die Hochtemperaturschritte zur Aktivierung der Dotierungsgebiete wurden bereits vorher durchgeführt.

Nachteilig ist der Erhöhte Aufwand bei der Fertigung, so muss beispielsweise vor dem Ätzen des Polysiliciums die Gate-Elektrode „geöffnet“ werden. Dies kann beispielsweise durch chemisch-mechanisches Polieren (CMP) ermöglicht werden. Die hohen Genauigkeiten und die unterschiedlichen Materialien machen den Prozess aber sehr anspruchsvoll. Denn ein nicht vollständig geöffnetes Gate behindert die Ätzung und ein überpoliertes Gate kann die elektrischen Eigenschaften des Transistors negativ beeinflussen. Zudem müssen alle Transistoren auf dem Wafer mit Durchmessern bis zu 300 mm möglichst gleichartig geöffnet werden.

Fully-Silicided-Gate-Prozess

Der Fully-Silicided-Gate-Prozess ist im Wesentlichen eine Weiterführung der Polysilicium-Gate-Technik. Hier werden Silicide zur besseren elektrischen Kontaktierung der Gate-Elektrode eingesetzt. Hergestellt werden diese, in dem auf die Polysiliciumschicht eine dünne Schicht aus einem Metall, beispielsweise Nickel, abgeschieden wird. In einem Hochtemperatur diffundieren die Metallatome in das Polysilicium ein und bilden an der Grenzfläche sehr gut elektrisch leitfähiges Silicid – früher Titan- und Cobaltsilicid und heute häufig Nickelsilicid – und mit einem geringen Kontaktwiderstand zu den metallischen Kontakten (meist aus Wolfram). Wie erwähnt wird diese Idee beim Fully-Silicided-Gate-Prozess weitergeführt und das gesamte Polysilicium in ein Silicid umgewandelt bzw. ersetzt (vergleichbar mit der Replacement-Metal-Gate-Technik). Dadurch wird das Problem der Gate-Verarmung gelöst. Streng genommen handelt es sich aber nicht wirklich um eine Metal-Gate-Technik. Bei der Polysilicium-Gate-Technik wird die Silicidherstellung in der Regel mit der Silicidbildung für die Source- und Drain-Kontakte kombiniert. Eine zu starke Silicidschicht in diesen Bereichen können jedoch negative Auswirkungen auf die Eigenschaften der Transistoren haben. Um dies zu verhindern wurden auch Prozesse vorgeschlagen, bei denen die beiden Silicidbildungen getrennt werden. Dabei müssen die Source- und Drain-Gebiete vor der Silicidbildung im Gate durch eine Deckschicht geschützt werden.[3]

Nachteilig ist die begrenzte Möglichkeit der Austrittsarbeitanpassung der Silicide, weswegen sich diese Methode bislang nicht durchsetzen konnte.

Aufbauvarianten und Materialien

Neben den Herstellungsvarianten gibt es auch verschiedene Varianten für den Aufbau des Gate-Stapels, beispielsweise:

- eine Metallschicht und eine Dielektrikumschicht (engl. single metal, single dielectric, SMSD): Der einfachste Aufbau, dabei wird jeweils getrennt für p-Kanal- und n-Kanal-FETs zunächst das Dielektrikum und dann das metallische Gate abgeschieden.

- eine Metallschicht und zwei Dielektrikumschichten (engl. single metal, dual dielectric, SMDD): Ähnlich wie SMSD, nur besteht das Dielektrikum aus zwei Schichten. Dies wird vor allem für eine verbesserte Grenzfläche mit geringeren Grenzflächenladungen oder für eine Verbesserung der Schichthaftung gemacht.

- zwei Metallschicht und eine Dielektrikumschicht (engl. dual metal, single dielectric, DMSD): Ähnlich wie SMSD, nur wird zur Anpassung der Austrittsarbeit eine weitere Metallschicht zwischen dem Dielektrikum und dem eigentlichen metallischen Gate abgeschieden.

- zwei Metallschichten und zwei Dielektrikumschichten (engl. dual metal, dual dielectric, DMDD): Eine Kombination von SMDD und DMSD.

Dieses Schema kann theoretisch beliebig fortgesetzt werden, jedoch steigt die Komplexität und damit der Herstellungsaufwand sehr stark an.

Typische Materialien für die Gate-Elektrode (nicht beim Fully-Silicided-Gate-Prozess) sind derzeit Titannitrid (TiN, für PMOS) bzw. Titanaluminiumnitrid (TiAlN, für NMOS). Für die Anpassung der Austrittsarbeit kommen verschiedene Materialien zum Einsatz, zu nennen sind hier vor allem dotiertes Hafniumoxid, Aluminiumoxid (Al2O3) und Lanthanoxid (LaO).

Vor- und Nachteile

Die Vorteile von HKMG liegen vor allem in drastischen Reduzierung des Gate-Leckstroms (Faktor größer 100) und der damit verbundenen Möglichkeit mikroelektronische Schaltkreise weiter zu skalieren. Damit verbunden ist eine geringere Versorgungsspannung und ermöglicht somit schnellere und energieeffizientere Transistoren herzustellen. Die HKMG-Technik macht somit aktuelle Spitzenprodukten (2011), mit Strukturbreite im Bereich von 28 nm und kleiner, erst möglich. So könnten HKMG-Prozessoren bei gleichem Design mit einer höheren Taktfrequenz betrieben werden als gewöhnlich gefertigte Prozessoren. In der Praxis wird jedoch eine solche Übertragung eines Prozessordesign in einen vollkommen neuen Fertigungsprozess nicht durchgeführt. Vielmehr werden bei jeder Technologiestufe und somit höherer Integrationsdichte auch neue Elemente in der Prozessorarchitektur eingeführt.

Der Aufwand bei der Fertigung ist im Vergleich zum vorher genutzten Polysilicium-Siliciumdioxid-Aufbau ungleich höher. So stiegen mit der HKMG-Technik nicht nur die Anzahl der notwendigen Prozessschritte, sondern es wurden auch höhere Anforderungen an die Fertigungstechniken gestellt und es mussten ganz neue Verfahren eingeführt werden. Ein Beispiel ist die Herstellung der High-k-Schichten: zu Beginn der Forschungsarbeiten wurden High-k-Schichten durch konventionelle Beschichtungsverfahren der chemischen und physikalischen Gasphasenabscheidung hergestellt. Damit konnten sehr gute, glatte und ausreichend dünne Schichten hergestellt werden. Die elektrischen Eigenschaften von so hergestellten High-k-Kondensatoren bzw. -Transistoren waren jedoch eher schlecht. Die Ursache des Problems lag in Ladungen an der Grenzfläche zwischen dem Siliciumsubstrat und der High-k-Schicht. Diese Grenzflächenladungen entstehen durch atomare Fehlstellen oder offene Bindungen. Sie fangen Ladungsträger ein und ändern beispielsweise die notwendige Spannung, die angelegt werden muss, um die Schwellspannung des Transistors zu erreichen. Ähnliche Probleme hatte man bereits in den 1960er Jahren mit Siliciumdioxid. Damals wurden die Probleme mit der Einführung der thermischen Oxidation von Silicium zur Herstellung der Oxidschicht gelöst. Für High-k-Materialien gibt es jedoch keinen vergleichbaren Beschichtungsprozess. Die Lösung lag diesmal in der Einführung eines Beschichtungsverfahrens, das die Herstellung von atomarglatten Schichten auf dem (ebenfalls atomarglatten) Siliciumsubstrat erlaubt, die Atomlagenabscheidung (ALD).[4]

Literatur

- Mark T. Bohr, Robert S. Chau, Tahir Ghani, Kaizad Mistry: The high-k solution. In: IEEE Spectrum. 44, Nr. 10, 2007, S. 29–35, doi:10.1109/MSPEC.2007.4337663 (Mit anschaulichen Darstellungen zu den zu lösenden Problemen, HTML).

- R. Chau, S. Datta, M. Doczy, B. Doyle, J. Kavalieros, M. Metz: High-κ/metal-gate stack and its MOSFET characteristics. In: Electron Device Letters, IEEE. 25, Nr. 6, 2004, S. 408–410, doi:10.1109/LED.2004.828570.

Weblinks

- Thomas Y. Hoffmann: Integrating high-k /metal gates: gate-first or gate-last?

- Intel (Hrsg.) Intel® Hi-k Metal Gate Silizium Technologie. Hintergrundinformation März 2009.

- Philipp Laube: High-k Metal Gate. halbleiter.org.

- D. James: An Ongoing History of Strain-Now Available with High-k! WeSRCH-Veröffentlichung (Vortragsfolien; sehr interessante Präsentation mit einer Vielzahl von TEM-Aufnahmen diverser Transistoren in 65- und 45-nm-Technik diverser Hersteller)

Einzelnachweise

- ↑ Howard R. Huff: High dielectric constant materials: VLSI MOSFET Applications. Springer, 2005, ISBN 9783540210818, S. 457 f.

- ↑ Mark T. Bohr, Robert S. Chau, Tahir Ghani, Kaizad Mistry: The high-k solution. In: IEEE Spectrum. 44, Nr. 10, 2007, S. 29–35, doi:10.1109/MSPEC.2007.4337663 (HTML).

- ↑ Howard R. Huff: High dielectric constant materials: VLSI MOSFET Applications. Springer, 2005, ISBN 9783540210818, S. 456.

- ↑ Mark T. Bohr, Robert S. Chau, Tahir Ghani, Kaizad Mistry: The high-k solution. In: IEEE Spectrum. 44, Nr. 10, 2007, S. 29–35, doi:10.1109/MSPEC.2007.4337663 (HTML).

Wikimedia Foundation.