- Silicon on Insulator

-

Der englische Begriff silicon on insulator (SOI, deutsch „Silizium auf einem Isolator“) bezeichnet eine Herstellungstechnologie für Schaltkreise auf Basis von Silizium-Substraten. Diese befinden sich auf einem isolierenden Material, wodurch sich kürzere Schaltzeiten und geringere Leistungsaufnahmen, besonders bezüglich der Leckströme, ergeben.

Die Technik wurde von IBM erstmals 1998[1] für ein kommerzielles Produkt angekündigt und erstmals von AMD für den AMD K8 [2] in der Großserienproduktion umgesetzt. Wichtige Hersteller von Prozessoren mit SOI-Technik sind Globalfoundries, Freescale und IBM.[3] Die Branchenführer Intel und TSMC haben bislang keine Produkte in SOI-Technik vorgestellt.

Inhaltsverzeichnis

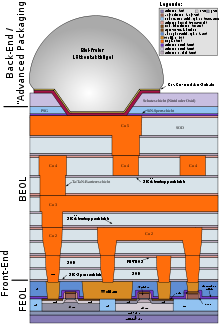

Aufbau und Herstellung

Im Gegensatz zu gewöhnlichen Transistoren, die direkt auf dem Silizium-Wafer gefertigt werden, haben die Transistoren auf einer Isolatorschicht eine geringere elektrische Kapazität, so dass die bis zum Schalten benötigten Ladungen verringert werden. Durch die so verringerten Schaltzeiten werden höhere Taktraten ermöglicht. Gleichzeitig wird so die Leistungsaufnahme verringert, wodurch sich auch eine geringere Verlustleistung ergibt, was beispielsweise einen Betrieb mit schwächerer und damit leiserer Kühlung möglich macht. Jedoch kam es zu erheblichen Verzögerungen bei der Entwicklung der ersten Großserie in SOI-Technik durch AMD, die in anfänglich zu hohen Kapazitäten und damit zu niedrigen Taktraten vermutet wurden. Ein weiterer Vorteil der SOI-Technik ist eine geringere Empfindlichkeit gegenüber ionisierender Strahlung.

In der Literatur werden eine Vielzahl von Herstellungsverfahren für SOI-Wafern beschrieben.[4] Dazu zählen verschiedene Verfahren die es ermöglichen eine dünne Siliziumschicht auf einem Wafer aus isolierenden Material herzustellen, beispielsweise Saphir (vgl. Silicon on Sapphire). Für die späteren Transistoren werden in der Regel Schichten aus einkristallinem Silizium benötigt/bevorzugt; Hauptgründe sind die deutlich besseren elektrischen Eigenschaften. Da bei den meisten Beschichtungsverfahren jedoch keine einkristalline Siliziumschicht abgeschieden wird (Ausnahme sind entsprechende Epitaxieverfahren), umfassen die SOI-Fertigungstechniken auch Rekristallisationsschritte.

Weitere Möglichkeiten SOI-Wafer herzustellen sind Verfahren, die auf Ionenimplatation basieren (z. B. SIMOX) oder spezielle Schichttransfertechiken wie „Smart Cut“. Bei der SIMOX-Technik (engl. separation by implanted oxygen) werden Sauerstoffionen in einen Silizium-Wafer eingebracht. Durch Ionenimplantation ist es möglich die Tiefe (wenige 100 nm) und die Breite (ca. 50 nm) des Bereich, in dem die Sauerstoffionen eingebracht werden, zu steuern. Um nun eine „vergrabene“ Siliziumdioxidschicht zu erzeugen, wird durch einen Hochtemperaturschritt der Kristall „ausgeheilt“, dabei reagiert der eingebrachte Sauerstoff (nach der Implantation hauptsächlich auf Zwischengitterplätzen) mit dem Silizium und bildet eine isolierende Schicht aus Siliziumdioxid. Ähnliche Techniken gibt es auch mit Stickstoff (engl. separation by implanted nitrogen, SIMNI) oder Kohlenstoff (engl. silicon carbide on insulator, SiCOI). Das sogenannte „Smart-Cut“-Verfahren, basiert ebenfalls auf der Ionenimplantation und nutzt zusätzlich das Waferbonden. Bei diesem Verfahren werden zunächst Wasserstoffionen in einen zuvor oxidierten Siliziumwafer eingebracht. Im nächsten Schritt wird dann dieser Wafer mit einem weiteren noch nichtoxidierten Wafer verbunden („bonden“). Anschließend wird der erste Wafer im Implantationsbereich der Wasserstoffionen gespalten (bei Temperaturen größer 500 °C wird in Zusammenhang mit den implantierten Wasserstoffionen eine mechanische Spannung im Wafer erzeugt, die diese Spaltung bewirken kann) und anschließend bis auf wenige Mikrometer abgedünnt.

Literatur

- Jean-Pierre Colinge: Silicon-on-Insulator Technology: Materials to VLSI. Springer, 1991, ISBN 978-0-7923-9150-0.

Weblinks

- AMD & SOI (Silicon on insulator) Special. Auf: AMDboard.com (zuletzt geprüft am 27.Februar 2008) – Informationen über die Entwicklung der SOI-Technik.

Einzelnachweise

- ↑ IBM Advances Chip Technology With Breakthrough For Making Faster, More Efficient Semiconductors

- ↑ Intel and Motorola/AMD's 130 nm processes to be revealed. Chip Architect, abgerufen am 27. Februar 2008.

- ↑ Christof Windeck: Globalfoundries entwickelt T-RAM mit. In: Heise-Online. 20. Mai 2009, abgerufen am 28. September 2009.

- ↑ Jean-Pierre Colinge: Silicon-on-Insulator Technology: Materials to VLSI. Springer Verlag, 1991, ISBN 978-0-7923-9150-0, S. 10ff.

Wikimedia Foundation.