- Strukturbreite

-

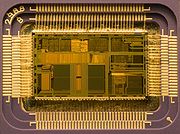

Die Strukturgröße oder auch Strukturbreite (man spricht auch von Prozess oder Technologie, wenn man das gesamte auf diese Sturkturgröße ausgerichtete Herstellungsverfahren meint) ist eine Größenangabe der Halbleitertechnik und beschreibt die Kantenlänge der bestimmenden (kleinsten) Plotter-Einheit. Es handelt sich dabei also um das Maskenmaß. Die Abmessungen der damit erzeugten Strukturen sind durch Unterbelichtung und Diffusion in der Regel etwas kleiner als die für die Maske benutzte Plotter-Einheit. Bei den kleinsten, auf einem Halbleiterträger erzeugten Strukturen handelt es sich üblicher weise um die Gate-Länge eines FETs.

Der Begriff wird auch im Bereich der digitalen, optischen Speichermedien verwendet, meist für die Abmessungen der Lands und Pits von Laser-Medien. Auch bei der Nanotechnologie, die sich eher in einem physikalisch-technischen Kontext mit Strukturen bis hinauf zu 100 nm beschäftigt, wird der Begriff angewandt.

Inhaltsverzeichnis

Bedeutung

Von der Angabe lässt sich grob auf die maximale Geschwindigkeit und die Verlustleistung des Bauteils rückschließen. Ebenfalls wird zusammen mit der Die-Größe bestimmt, wie komplex der Halbleiter ist, d. h. wie viele Transistoren er tragen kann. Für einzelne, große Transistoren (z. B. MOSFETs) ist die Angabe prinzipiell ebenfalls zutreffend, jedoch weitaus weniger aussagefähig, da diese, um hohe Leistung zu erreichen, eher groß sein sollen.

Zusammen mit den Bemühungen von Forschung und Industrie, die Wafer-Größe bei der Halbleiterfertigung zu steigern, bildet dieses Element einen der zentralsten Aspekte der Weiterentwicklung der Halbleitertechnik im Rennen um die Erhaltung des Moore’schen Gesetzes, einer Faustregel nach der sich die Leistung von Halbleitern bislang über der Zeit weiter entwickelt hat.

Die Strukturgröße ist ein wichtiger Parameter, der zentral vom verwendeten Halbleiterprozess (CMOS, NMOS, TTL etc.) und dem dafür verfügbaren kleinsten bzw. gewählten Transistordesign bestimmt wird. Hierbei sind sowohl die Materialbeschaffenheit des Trägers, meist ein Silizium-Wafer, und der Dotierungen, als auch die eingesetzte Lithographietechnik und damit die erforderlichen Fertigungsparameter wie etwa Luftreinheit und ähnliches bis hin zur momentanen Verfügbarkeit von Fabrikkapazitäten wichtig. Auch auf den Preis solcher Produktionsleistungen lässt sich daraus in der Regel zurück schließen.

Nicht zuletzt bestimmt die Strukturgröße wie viele Transistoren auf einen Wafer passen und damit auch wie viele einzelne Halbleiter typisch daraus gewonnen werden können. Zusammen mit dem logischen Design des Halbleiters ergibt sich also eine Zahl an Chips je Wafer, die maßgeblich in die Chipfläche und somit in den Preis eingeht. So besitzen beispielsweise NOR-Flashs technologiebedingt bei gleicher Strukturgröße geringere Speicherkapazitäten als NAND-Flashs, da ihre Speicherzellen mehr Transistoren und damit Platz auf dem Die erfordern.

Bei sogenannten Die-Shrinks geht es darum, die Strukturgröße unter Beibehaltung der Halbleiterfunktionalität gegen eine kleinere auszutauschen. Ein und dasselbe funktionale Design kann somit in mehreren verschiedenen Strukturgrößen produziert werden. Die kleineren Strukturen weisen oftmals eine ihrer Transistor-Technologie entsprechende geringere Verlustleistung im Ruhezustand und bei Schalthandlung auf, so dass die für Halbleiter typisch erreichbare maximale Taktrate bei kleineren Strukturen für gewöhnlich höher ist. Wird die Die-Größe dagegen beibehalten, dann ergeben sich Möglichkeiten zur Erweiterung von skalierbaren Einheiten, z. B. der Caches eines Prozessors.

Bei kleineren Strukturen muss der jeweilige Hersteller zunächst einige Schritte zur Prozessoptimierung unternehmen um die bis dahin üblichen Ausbeuten wieder zu erreichen. Entsprechend ist ein Umstieg auf eine Technologie mit kleinerer Strukturgröße immer auch mit Kosten und Risiken verbunden. Es wird natürlich versucht, diese durch geeignete Forschungen und Erprobungen bereits im Vorfeld möglichst gering zu halten, um möglichst frühzeitig eine wirtschaftliche Effizienz erreichen.

Historie

Lange Zeit wurde diese Größe in der Einheit Mikrometer verwendet, wobei zuletzt Ziffern mit vorangestellter Null-Komma verwendet wurden. Mittlerweile ist hierbei der zweistellige Nanometerbereich erreicht worden, so dass sich die Angabe nun wieder leichter handhaben lässt.

Selbst in Fachkreisen kam es gelegentlich fälschlich zur Weglassung der führenden Null-Komma-Sequenz in Fließtexten, als der Schritt unter die Strukturgröße 1 µm getätigt wurde. Es wurde dann statt von einer 0,14-µm-Struktur nur noch verkürzend von einer 14er-Struktur gesprochen.

Name Hersteller Jahr Technologie Strukturgröße 4004-Prozessor Intel 1971 PMOS 10 µm NMOS-Logik 6 µm HMOS-Halbleiter 1,5 µm i386DX Intel 1984 1,5 µm i486DX2-66 mit P24-Kern Intel 1992 0,8 µm Pentium P5 Intel 1993 BiCMOS 0,8 µm Pentium P55C Intel 1997 CMOS 0,35 µm Athlon (K7) AMD 1999 0,25 µm bis 0,18 µm VIA C3 (C5B-Revision) VIA 2001 0,15 µm 256-MBit-Speicherchip Infineon 2002 0,14 µm Storm-1 (DSP) SPI 130 nm NEC und TSMC 2001 100 nm 2007 65 nm Intel Core 2 Duo Intel 2007 45 nm XTREME (Jenoptik und Ushio, gefördert von Intel) um 2009 Extrem-Ultraviolett-Lichtquellen anfangs: <40 nm,

2009: 32 nm,

später: 13,5 nmSpeicher mit 45 GByte/cm2 Universität Tokyo 2004 Optischer Speicher 35 nm 2009 Nanoröhren-Transistor 18 nm Lacke Sematech 2006 Start neuer Forschungsbemühungen Ziel: 13,5 nm MIT 2008[1] Lithografietechnik 25 nm Einzelnachweise

- ↑ Christof Windeck: MIT-Forscher zeigen Lithografietechnik für 25-nm-Strukturen. Auf: Heise Online. 11. Juli 2008 (Nachrichtenmeldung)

Weblinks

- Wettlauf um neue Lithografie-Techniken verschärft sich, heise-Verlag, 2001: Bericht zur SPIE Microlithography conference mit Prognosen zur erwarteten Entwicklung – wurde durch die Realitäten bereits 2007 überholt.

- Sematech nimmt Forschungszentrum für EUV-Lithografie-Lacke in Betrieb, heise-Verlag, 2006: Lackentwicklung für Strukturgrößen bis 13,5 nm; Intel-EUV-Serienproduktion für 2009 geplant

Wikimedia Foundation.