- Chip-On-Board-Technologie

-

Die Chip-on-Board-Technologie (Abk.: COB, deutsch Nacktchipmontage) ist eine Technologie zur Direktmontage von ungehäusten Halbleiter-Chips auf Leiterplatten zu einer elektronischen Baugruppe.[1] Heute verwendet man den Begriff COB für alle Baugruppen, die den nackten Halbleiter beinhalten, während man darunter ursprünglich ausschließlich Baugruppen mit Chip-and-Wire-Technik verstand.

Inhaltsverzeichnis

Montagevarianten

Bei der Montage von ungehäusten Halbleiter-Chips werden zwei Varianten unterschieden:

- Direct Chip Attach – der Chip wird direkt auf dem Substrat befestigt;

- Tape-Automated Bonding – Technik, bei der der Chip auf einen Zwischenträger vormontiert wird, der bei der fertig zusammengefügten Baugruppe die Verbindung zum Substrat herstellt.

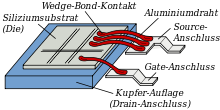

Kontaktierung am Beispiel eines Leistungstransistors, dabei wurde der Gate- bzw. der Source-Anschluss durch Drahtbonden und der Drain-Anschluss durch Chipbonden realisiert

Kontaktierung am Beispiel eines Leistungstransistors, dabei wurde der Gate- bzw. der Source-Anschluss durch Drahtbonden und der Drain-Anschluss durch Chipbonden realisiert

Die erste Montagevariante Direct Chip Attach, also die direkte Montage des ungehäusten Halbleiter-Chips auf den Verdrahtungsträger, kann mithilfe unterschiedlicher Techniken erfolgen:

- Entweder mithilfe der Chip-and-Wire-Technik, bei der der Chip direkt auf die Leiterplatte geklebt und mittels Drahtbrücken mit dem Leiternetzwerk elektrisch verbunden wird. Dabei befinden sich die Kontaktflächen des Chips auf der von der Leiterplatte abgewandten Seite des Chips.

- Oder man montiert den Chip mithilfe der Flip-Chip-Technik, bei der vorher auf die Kontaktflächen des Chips aufgebrachte Lotkugeln oder leitfähige Kunststoffhügel den Chip mit dem Verdrahtungsträger elektrisch und mechanisch verbinden. Die Kontakte des Chips sind dabei der Leiterplatte zugewandt.[1]

Arbeitsschritte bei der Direktmontage mittels Chip-and-Wire-Technik:

- Chipbonden: Bezeichnet das Bestücken und Kleben solcher Bauteile auf den Träger.

- Drahtbonden: Das Verbinden der Drähte (Gold, Aluminium, seltener Palladium, Kupfer) vom Chip zum Träger (PCB/Platine, Keramik, Flexprint, Glas, sonstige).

- Chip-Verguss (engl. glob top): Das Vergießen der kontaktierten Chips.

Bei der zweiten Variante, Tape Automated Bonding, wird der Chip auf einem Zwischenverdrahtungsträger vormontiert und mit diesem zusammen auf der Leiterplatte montiert.[1]

Vor- und Nachteile

Als Vorteil dieser Technologie ergibt sich eine höhere Taktfrequenz aufgrund von kürzerer Wege zwischen Chip und Leiterplatte. Weiterhin kommt es zu einer besseren thermischen Anbindung zwischen dem Chip und der Leiterplatte, hierbei trägt das Vergussmaterial ebenfalls zur Wärmeableitung auf die Leiterplatte bei. Im Vergleich zu Chips im Gehäuse benötigt diese Technologie weniger Platz, was eine höhere Integrationsdichte auf der Leiterplatte ermöglicht. Im Großserienprozess kann diese Technologie preiswert hergestellt werden. Darüber hinaus kann mit dieser Technologie durch Parallelschaltung mehrerer Bonddrähte ein geringer elektrischer Widerstand realisiert werden, was im Bereich der Leistungselektronik zu geringeren thermischen Verlusten führt.

Als Nachteile ergeben sich bei dieser Technologie die fehlende Möglichkeit einer Reparatur eines defekten Chips. Weiterhin ist zur Verarbeitung dieser Bauelemente ein Reinraum (weitgehend staubfrei und klimatisiert) erforderlich.

Anwendung

Anwendung findet die Chip-on-Board-Technologie in Großserien und Billiganwendungen (Uhren, Taschenrechnern). 1996 ging man davon aus, dass im Jahr 2000 15 % aller hergestellten integrierte Schaltkreise mittels der Chip-on-Board-Technik montiert würden.[2] Der Anteil der mithilfe der Chip-on-Board-Technologie gefertigten elektronischen Baugruppen an allen weltweit gefertigten Baugruppen betrug dabei im Jahr 1995 gerade einmal 0,1 %.[3]

Einzelnachweise

- ↑ a b c Wolfgang Scheel (Hrsg.): Baugruppentechnologie der Elektronik - Montage. 2. Auflage. Verlag Technik, Berlin 1999, ISBN 3-341-01234-6, S. 13.

- ↑ E. Meusel und B. Lauterwakd: Nacktchipverarbeitung durch Löten – Trends und technologische Probleme. In: DVS-Berichte Band 182: Weichlöten in Forschung und Praxis 1996. 1996, S. 1

- ↑ „The National Technology Roadmap For Electronic Interconnections. PC 1995“ zitiert In: Wolfgang Scheel (Hrsg.): Baugruppentechnologie der Elektronik - Montage. 2. Auflage. Verlag Technik, Berlin 1999, ISBN 3-341-01234-6, S. 12/13.

Kategorie:- Aufbau- und Verbindungstechnik der Elektronik

Wikimedia Foundation.