- Boundary Scan Test

-

Boundary Scan und Grenzpfadabtastung sind synonyme Begriffe für ein standardisiertes Verfahren zum Testen digitaler und analoger Bausteine in der Elektronik.

Heutzutage ist es üblich, die Verschaltung von Platinen mehr auf zusätzliche innere Verbindungsleitungen zu führen. Sogenannte Mehrlagenplatinen (engl. multilayer PCBs) können bis zu 20 solche Verdrahtungsebenen besitzen. Außerdem werden Integrierte Schaltungen (IS) mit sehr vielen Pins häufig in Gehäusen geliefert, die einen mechanischen Zugriff unmöglich machen, da sämtliche Anschlüsse unter dem Gehäuse verborgen sind. Es war also notwendig, Leiterplatten ohne direkten physischen Zugang zu prüfen, wie es zum Beispiel bei einem In-Circuit-Test notwendig ist. Das als Boundary Scan bekannte Verfahren wurde vorwiegend in Europa (Philips) entwickelt und ist inzwischen international genormt.

Die Boundary Scan-Methode verwendet zusätzliche Zellen (Latches), mit deren Hilfe Signale über vordefinierte Pfade von außen in die zu testende Schaltung injiziert werden können. Die Signale aus der Schaltung, die an Pins der IS anliegen, können über den Scanpfad erfasst werden. Im Normalbetrieb sind die Latches passiv. Es besteht kein Unterschied zu IS ohne Boundary Scan Funktionalität die Anschlüsse des Chip sind nur mit den Pins der IS verbunden. Im Testbetrieb werden sie dem Verfahren entsprechend aktiv gesteuert.

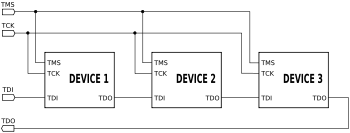

Um die Anwendung der Boundary Scan-Methode in einer integrierten Schaltung zu ermöglichen, werden (mindestens) an den Ein- und Ausgängen hochintegrierter Bausteine entsprechende spezielle Modifikationen eingebaut. Dabei ist an jedem Ein- oder Ausgang einer IS eine Boundary-Scan-Zelle eingebaut. Alle Boundary Scan Zellen sind seriell zu einer Kette verknüpft, welche die gesamte I/O-Struktur der Integrierten Schaltung umfasst. Die IS besitzt mindestens vier eigens reservierte Steuerungs- und Daten-Pins. Dabei handelt es sich um Testdaten-Eingang (TDI) und –Ausgang (TDO), einen Test-Takt (TCK) und einen Test-Mode-Select-Anschluss (TMS) sowie den optionalen Test-Reset-Eingang (TRST). Diese Pins ergeben den Test Access Port (TAP). Hierbei handelt es sich um einen synchronen endlichen Automaten (engl. finite state machine, FSM) mit 16 möglichen Zuständen.

Über TDI/TDO werden die Testdaten weitergegeben. TMS dient zur Verteilung von Steuerbefehlen, welche individuell für jede Integrierte Schaltung den gewünschten Test-Modus einstellen. Mit der steigenden Flanke von TCK werden jeweils die externen Daten von TDI in die entsprechenden Register eingelesen. TRST dient zum initialisieren der FSM.

Die eigentliche Scankette beginnt mit dem TDI Eingangspin der Schaltung. Dieser wird über den Stecker auf der Leiterplatte mit dem TDO des Boundary Scan Testgeräts verbunden. Die Kette wird durch Verbinden der TDO-Ausgänge der einzelnen IS jeweils mit TDI des nächsten IS fortgesetzt. Am Ende der Kette wird über den Stecker der letzte TDO Ausgang mit TDI des Boundary Scan Testgeräts verbunden. TMS, TCK und optional TRST werden parallel von allen IS mit den entsprechenden Pins am Stecker verbunden.

TDI- und TDO-Daten werden über eine Schiebe-Funktion in die Eingangs-Scan-Zellen (Scankette, siehe Scan Test) seriell ein- bzw. ausgeschoben. Wenn alle TDI-Daten eingetaktet sind, werden sie in die zu testende Schaltungs-Anordnung parallel ausgegeben. Das Antwort-Signal kann dann von den Ausgangs-Scan-Zellen erfasst werden und seriell ausgelesen werden. Die Scan-Zellen befinden sich meist an den I/O-Pins, welche dadurch umgangen werden können. Durch das Boundary-Scan-Prinzip vermeidet man das Kontaktieren einer großen Anzahl von Pins, und damit mögliche Kontaktfehler, und erreicht leicht (Teil)Schaltungen im Inneren eines Chips. Meist wird eine Vielzahl von Scanketten (scan chains) parallel betrieben.

Mit Hilfe der Boundary Scan Funktionalität können Verbindungen zwischen Pins mit Boundary Scan Funktion geprüft werden. Ebenso ist es möglich, Kurzschlüsse zwischen diesen Pins festzustellen. Mit Hilfe der Boundary Scan Ausgangszellen können auch externe programmierbare Speicher programmiert werden. Typischerweise handelt es sich hierbei um Flash-Speicher. Begründet durch den Umweg über die Scankette ist dieses Verfahren aber langsamer als andere Programmierverfahren. Dies ist somit geeignet, um kleinere Datenmengen zu programmieren. Flüchtige Speicher können durch Programmieren und anschließendes Auslesen von Bitmustern über die Boundary Scan Zellen überprüft werden. Dadurch können die Lötverbindungen dieser IS geprüft werden. Dieses Verfahren wird beispielsweise bei RAM Speichern verwendet.

Der JTAG-Standard IEEE 1149.1 legt die Spezifikationen des TAP-Busses sowie der Scan-Zellen fest. Dieser Standard wird durch den P1500-Standard zum Backplane-Testen ergänzt, um viele unterschiedliche Systeme in einer elektronischen Einheit über dieselbe Schnittstelle zu testen.

Für den Test von analogen Signalen wurde inzwischen der JTAG-Standard IEEE 1149.4 definiert.

AC-gekoppelte oder differenzielle Signale können unter Verwendung des JTAG-Standard IEEE 1149.4 getestet werden.

Funktionelle Erweiterungen

Über die reine Testfunktion hinausgehend bieten viele Speicherbausteine mit Boundary Scan über den TAP-Bus auch Möglichkeiten, den betreffenden Baustein in der Schaltung (engl. in-circuit) zu programmieren. Bei Mikroprozessoren können über die meist als JTAG-Schnittstelle bezeichnete Verbindung auch Diagnoseprogramme zum Debuggen und Fehlersuchen laufen. Damit ist der Einsatz spezieller und meist teurer In-Circuit-Emulatoren hinfällig. Alle diese Erweiterungen sind allerdings durch spezielle, meist nicht dokumentierte Befehle am TAP-Bus realisiert und sind stark hersteller- und bausteinspezifisch.

Integration

Jedes Testverfahren hat seine Grenzen bezüglich Testabdeckung und Fehlererkennung bzw. Diagnose. Hinzu kommt die zunehmende Komplexität aktueller und vor allem zukünftiger Baugruppen. Bauformen wie BGA, µBGA oder Flip Chip lassen kaum noch Möglichkeiten eines mechanischen Zugriffs zu. Um eine optimale bzw. maximale Testtiefe zu erreichen, ist es daher sinnvoll Prüfverfahren miteinander zu kombinieren. Boundary Scan kann als Option zur größeren Test- und Fehlerabdeckung in ATE-Systeme wie In-Circuit-Tester, Flying Probe Tester, MDA, Funktionstestsysteme oder AOI-Systeme integriert werden.

Weblinks

Wikimedia Foundation.