- Damascene-Prozess

-

Der Damascene-Prozess ist ein Fertigungsprozess aus der Halbleitertechnik. Er beschreibt eine Fertigungsvariante von integrierten Schaltkreisen (Mikrochips) mit Kupfer-Leiterbahnen.

Der Name „Damascene“ stammt von einer antiken Verzierungstechnik, der Tauschierung (auch Damaszierung, engl.: damascening).

Inhaltsverzeichnis

Hintergrund

In den Anfangsjahren der Mikroelektronik (bis Anfang 2000er-Jahre) wurde ausschließlich Aluminium als Leiterbahnmaterial genutzt. Für die Herstellung der sogenannten Metallisierungsebenen (bestehend aus einer strukturierten Schicht für die Zwischenkontakte und einer weiteren Schicht mit den eigentlichen Leiterbahnen) wurde das Aluminium zunächst ganzflächig aufgebracht und anschließend über ein Trockenätzverfahren strukturiert. Da für Kupfer kein vergleichbarer Ätzprozess zur verfügung steht, konnte diese Verfahrensweise mit dem Umstieg einiger Unternehmen Anfang der 2000er Jahre zur sogenannten Kupfer-Technologie, bei der das Aluminium als Leiterbahnmaterial durch Kupfer ersetzt wurde, nicht übernommen werden.

Als alternatives Herstellungsverfahren wurde der Damascene-Prozess bzw. seine Weiterentwicklung der Dual-Damascene-Prozess entwickelt. Im Gegensatz zum Damascene-Prozess werden beim Dual-Damascene-Prozess die VIAs (engl.: Vertical Interconnect Access, Kontaktverbindungen zwischen zwei Metallisierungsebenen) und die darüberliegende Metallisierungsebene gemeinsam in einem Prozessschritt mit Kupfer gefüllt. Somit ist auch nur ein Kupfer-CMP-Schritt notwendig, bei dem das nach der Abscheidung (galvanisch) überstehende Kupfer, eingeebnet wird.

Verfahren

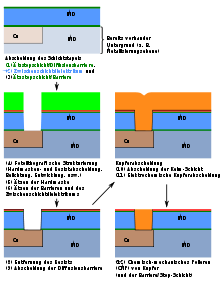

Ausgehend von einem vorhandenen Substrat, beispielsweise Silizium oder bereits abgeschiedene Metallisierungsebenen, wird zunächst eine Isolationsschicht (Dielektrikum), häufig Siliziumdioxid (SiO2) und eine dielektrische Kupfer-Diffusionsbarriere (beispielsweise Siliziumnitrid), ganzflächig abgeschieden. Es folgt eine fotolithografische Strukturierung, das heißt, es wird ein Fotoresist (Fotolack) aufgetragen und strukturiert. Die nun vorliegende strukturierte Fotoresistschicht dient als Maskierung für den nachfolgenden Trockenätzprozess, mit dem die späteren Kontaktlöcher bzw. Leiterbahnen freigeätzt werden. Anschließend wird der Fotoresist wieder entfernt.

Nach dieser Strukturierung folgt das Füllen der geätzten Gräben mit Kupfer (leitendem Material). Da Kupfer leicht in die Zwischenmetalldielektrika (inter metal dielectric, IMD, auch inter layer dielectric, ILD) diffundiert[1] diffundiert, ist es notwendig vor der Kupferabscheidung eine Diffusionsbarriere aufzutragen. Diese Diffusionsbarriere muss elektrisch leitfähig sein, da die Barriere auch am Boden der VIAs, das heißt an der Kontaktstelle zweier Metallisierungsebenen, aufgetragen wird.

Die Kupferabscheidung selbst kann sowohl über eine elektrochemische Abscheidung oder eine metallorganische chemische Gasphasenabscheidung (MOCVD) erfolgen. Beide Verfahren erfolgen wiederum ganzflächig, außerdem werden die Gräben „überfüllt“, so soll sichergestellt werden, dass keine Hohlräume zur nächsten Metallisierungsebene entstehen; der elektrische Kontakt wäre dann nicht sichergestellt bzw. würde einen höheren Widerstand aufweisen. Das überschüssige Kupfer wird anschließend durch chemisch-mechanisches Polieren (CMP) entfernt und eingeebnet.

Abschließend erfolgt nochmals die Abscheidung einer Barriereschicht, da anderenfalls das Kupfer leicht in höhere Ebenen diffundieren könnte. Da die Diffusionsbariere wiederum ganzflächig abgeschieden und nicht weiter strukturiert wird, muss sie aus einem nichtleitenden Material bestehen (z. B. Siliziumnitrid). Andernfalls könnten Kurzschlüsse zwischen den Leiterbahenen einer Metallisierungsebene entstehen. Die Barriereschicht wirkt gleichzeitig auch als Passivierungsschicht, das heißt, sie schützt das Kupfer vor der Umgebung. Dies ist notwendig da Kupfer leicht oxidiert. Anders als Aluminium bildet es aber kein schützendes Oxid. Das Kupferoxid ist durchlässig für Wasser und Sauerstoff, so dass mit der Zeit das gesamte Kupfer oxidieren würde, wodurch die Leiterbahnen unbrauchbar werden.

Literatur

- Shyam P. Murarka, Moshe Eizenberg, Ashok K. Sinha (Hrsg.): Interlayer Dielectrics for Semiconductor Technologies. Elsevier/Academic Press Inc., Amsterdam u. a. 2004, ISBN 0-12-511221-1, S. 218ff.

Weblinks

- Phillipp Laube: Kupfertechnologie. In: Halbleiter.org. 20. Oktober 2009, abgerufen am 24. November 2009.

Einzelnachweise

- ↑ S. P. Murarka, S. W. Hymes: Copper metallization for ULSI and beyond. In: Critical Reviews in Solid State and Materials Sciences. 20, Nr. 2, 1995, ISSN 1040-8436, S. 87–124.

Wikimedia Foundation.