- Complex Programmable Logic Device

-

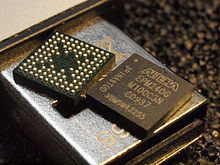

Eom Altera MAX 7000-series CPLD mit 2500 Gattern.

Eom Altera MAX 7000-series CPLD mit 2500 Gattern.

CPLD steht für Complex Programmable Logic Device. Die Technologie eigenspezifischer ICs ist seit den 60er Jahren bekannt, als Harris Semiconductor einen Baustein herausbrachte, dessen wesentlicher Bestandteil eine programmierbare Diodenmatrix (Fuse Configurable Diode Matrix) war. 1978 kamen die ersten vollständig konfigurierbaren Logikbausteine namens PLA (Programmable Logic Array) mitsamt Programmiersprache PALASM auf den Markt.

CPLDs bestehen im Wesentlichen aus folgenden Elementen:

- programmierbare AND/OR-Matrix

- programmierbare Rückkopplung

- Eingabeblock

- Ausgabeblock

Ein-/Ausgabeblöcke können schnelle Speicher, wie Latches, D-Flipflops oder Register, sein. In vielen modernen PLDs stehen programmierbare Ausgänge zur Verfügung, denen man definierte Zustände (active low, active high, tristate) zuweisen kann. Der AND/OR-Matrix als Kern kann jede beliebige kombinatorische Verknüpfung zugewiesen werden.

Ein CPLD setzt sich aus vielen SPLDs (simple programmable logic device) zusammen. Diese werden Makrozellen genannt. Die einzelnen SPLDs werden wiederum über Busse miteinander verbunden. Der homogene Aufbau ermöglicht eine exakte Bestimmung der Durchlaufzeiten, was den wesentlichen Unterschied zu den FPGAs ausmacht. Ein weiterer, allerdings nicht grundlegend notwendiger Unterschied ist die Konfiguration: Durch Fertigung in EECMOS electronically erasable complementary metal oxide semiconductor bleibt nach der Konfiguration das Programm im CPLD und muss nicht bei jedem Start neu geladen werden. Dieses Kriterium der Konfiguration ist kein wesentliches Unterscheidungsmerkmal zwischen CPLDs und FPGAs, allerdings ist es derzeit technologisch noch nicht möglich, die wesentlich komplexeren FPGA-Strukturen gemeinsam mit EEPROM-Zellen wie bei einem CPLD auf einem Chip unterzubringen. Am Markt befindliche rekonfigurierbare FPGA-Bausteine ohne externen Speicher sind derzeit (Mitte 2007) so genannte Multi-Die-Lösungen. Dabei werden mehrere, technologisch unterschiedlich hergestellte Halbleiterchips wie ein herkömmlicher SRAM-basierender FPGA-Chip und ein Flash-Konfigurationschip gemeinsam in einem Chipgehäuse untergebracht. Nach außen hin wird dann für das FPGA kein externer Speicher mehr benötigt.

Zwei CPLDs in MBGA-Bauweise auf einem USB-Stecker

Zwei CPLDs in MBGA-Bauweise auf einem USB-Stecker

Durch die hohe Anzahl von Eingängen / Logikblock bieten sich CPLDs vor allem für die Lösung komplexer, paralleler kombinatorischer AND/OR-Logik an wo viele Ein- bzw. Ausgänge vorhanden sind. Gleichzeitig sollte die Anzahl der notwendigen Speicher (Flipflops) bei der Anwendung von CPLDs minimal sein, da pro Ein- bzw. Ausgabepins meist nur ein einziges Flipflop als Register zur Verfügung steht. Digitale Schaltungen welche viele Register erfordern, wie beispielsweise Schieberegister oder digitale Zähler, lassen sich daher nur bis zu einem gewissen Grad in CPLDs effizient realisieren.

Bei steigender Zahl der Zellen werden die Makrozellen mit lokalen Leitungen zu übergeordneten Strukturen wie Logic Array Blocks, LABs zusammengefasst. Diese Bezeichnungen variieren allerdings je nach Hersteller.

Hersteller sind beispielsweise Xilinx, Altera, Lattice, Actel, Lucent, Cypress, Atmel oder Quicklogic.

Weblinks

Kategorie:- Programmierbare Logik

Wikimedia Foundation.