- Speichersegment

-

Unter Segmentierung versteht man bei der Speicherverwaltung in einem Betriebssystem die Unterteilung des benutzten Speicheradressraums in einzelne Segmente. Zweck der Unterteilung ist meist die Implementierung von Schutzmechanismen oder virtueller Speicherverwaltung. Je nach Betriebssystem und zugrundeliegender Hardware können einem Segment verschiedene Attribute zugewiesen werden. So können beispielsweise Programm-, Daten- und Stack-Segmente festgelegt werden. Die Speicherverwaltung sorgt dann unter anderem dafür, dass aus dem Programmsegment nur Befehle aber keine Daten gelesen werden, oder dass Daten im Datensegment nicht als Befehle interpretiert werden. Oft ist es auch möglich, Segmenten Privilegierungsebenen zuzuweisen, sodass auf die entsprechenden Segmente nur von Programmen bestimmter Privilegierungsebenen zugegriffen werden kann. Man kann so zum Beispiel Betriebssystemdaten und -befehle vor Zugriff durch andere Programme schützen. Häufig kann auch die Zugriffsart (zum Beispiel nur lesen, nur schreiben, kein Zugriff) eingeschränkt werden. Manche Systeme erlauben auch Privilegierungsebenen-abhängige Zugriffsarteneinschränkung.

Inhaltsverzeichnis

Speicheradressierung bei der Segmentierung

Ein Segment wird über zwei Werte definiert:

- Segmentanfangsadresse, Segmentbasis oder Basis: die erste im Segment enthaltene Speicheradresse

- Segmentlänge, Segmentlimit oder Limit: die Zahl der aufeinanderfolgenden Speicheradressen, die das Segment umfasst.

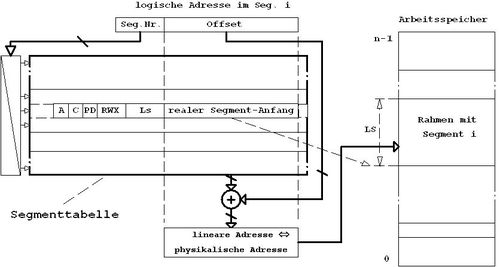

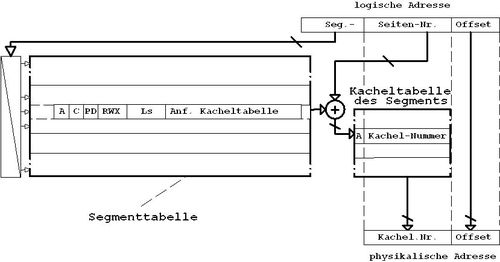

Segmentiert wird in der Regel der physische Adressraum direkt oder ein virtueller linearer Adressraum, der auf den physischen Adressraum abbildet. Durch die Segmentierung wird ein sogenannter logischer Adressraum gebildet. Logische Adressen sind unterteilt in einen Segmentselektor und einen Offset. Der Segmentselektor bestimmt direkt oder indirekt, über eine Segmentverwaltungstabelle, das adressierte Segment und somit die Segmentanfangsadresse und -länge. Der Offset gibt, relativ zum Segmentanfang, die Speicherstelle innerhalb dieses Segmentes an.

Soll aus einer logischen Adresse die lineare Adresse bestimmt werden, werden zunächst über den Segmentselektor die Segmenteigenschaften Basis, Länge, Typ, Lese-/Schreibrechte usw. ermittelt. Danach wird anhand der ermittelten Segmenteigenschaften geprüft, ob der Speicherzugriff zulässig ist. Weiterhin wird der Offset mit der Segmentlänge verglichen, um sicherzustellen, dass der Zugriff innerhalb der Segmentgrenzen liegt. Schlägt eine dieser Überprüfungen fehl, wird eine Fehlerbehandlung (Interrupt, Prozessor-Exception etc.) eingeleitet. Der Offset wird zur Segmentbasisadresse addiert und ergibt die lineare Adresse. Ist der lineare Adressraum nicht der physische, wird die lineare Adresse durch eine anschließende Seitenverwaltung (eng. "paging unit") in eine physische Adresse umgewandelt.

Diese Adressumwandlungen werden in modernen Computern üblicherweise von Speicherverwaltungseinheiten übernommen, welche in vielen modernen Prozessoren integriert sind.

Beispiele

Intels x86er im Real-Mode

Beim 8086-Prozessor und neueren x86ern im Real Mode wird die Segmentanfangsadresse direkt aus dem Segmentselektor der logischen Adresse berechnet. Alle Segmente haben die feste Länge von 64 KB. Eine logische Adresse wird in Real-Mode-Programmen meist so geschrieben: Segment:Offset, wobei Segment und Offset 16-Bit-Zahlen sind und in der Regel im Hexadezimalsystem angegeben werden, also zum Beispiel: 2F10:87A1.

Diese logische Adresse wird folgendermaßen in eine physische umgerechnet:

Adresse physisch = Segmentselektor logisch · 16 + Offset logisch

Im Beispiel ergibt sich für die physische Adresse:

0x2F10 · 16 + 0x87A1 = 0x2F10 · 0x10 + 0x87A1 = 0x2F100 + 0x87A1 = 0x378A1

Mit dieser Adressierung kann man die physische Adressbreite auf 20 Bit ausweiten, da die 16-Bit-Segmentadresse durch die Multiplikation mit 16 zu einer 20-Bit-Zahl wird, zu der noch der Offset addiert wird. Mit diesen 20 Bit können immerhin bis zu 1 MB RAM auf einem 16-Bit-Prozessor adressiert werden. Genaugenommen können unter bestimmten Umständen durch den Übertrag bei der Addition sogar 21-Bit-Zahlen bei der Adressrechnung entstehen, es kann also etwas mehr als 1 MB Speicher adressiert werden. Für genauere Informationen hierzu sei auf die Artikel High Memory Area und A20-Gate verwiesen.

Intels x86er im Protected-Mode

Ab Intels 80286-Prozessor wurde der sogenannte Protected Mode eingeführt. Hier können Segmente zwischen einem Byte und 64 KB (ab dem 80386er bis zu 4 Gigabyte) lang sein und an beliebigen Byte-Positionen im linearen Adressraum beginnen. Jedes Segment wird durch eine spezielle Datenstruktur, Segmentdeskriptor genannt, beschrieben. Neben der Segmentbasisadresse und der Segmentlänge enthält ein Segmentdeskriptor auch Informationen über Segmentattribute wie Segmenttyp, Privilegierungsebene und Lese-/Schreibrechte. Segmentdeskriptoren werden aus im Arbeitsspeicher liegenden Deskriptortabellen gelesen. Diese Tabellen werden vom Betriebssystem aufgebaut und verwaltet. Der Segmentselektor einer logischen Adresse gibt die Deskriptortabelle und den Index eines Segmentdeskriptors innerhalb der Tabelle an. Aus dem gewählten Segmentdeskriptor werden dann die zur Adressberechnung nötigen Daten ausgelesen.

Geschichte

Die Segmentierung war früher eine besonders wichtige Möglichkeit, mehr Speicher zu adressieren, als es durch die vorhandenen Adressleitungen bzw. die Größe (Anzahl Bits) von Prozessor-Registern allein möglich war. Auch zur Auslagerung von ganzen Prozessen und für den Speicherschutz wurde die Segmentierung eingesetzt. Durch leistungsfähigere Prozessoren wurde es aber durch das Paging zu Segmentierung mit Seitenadressierung (segmentation with paging) erweitert, das eine feinkörnigere und flexiblere Verwaltung des Speichers ermöglichte. Gängige Betriebssysteme machen von den Mechanismen des Segmentierens im 64-Bit-Modus keinen umfassenden Gebrauch mehr und nutzen statt dessen ausgiebig das Paging. Lediglich der Betriebssystemkern ist durch ein mit höheren Rechten privilegiertes Daten- und Codesegment von den anderen Programmen getrennt („Protected Flat Model“).

Wikimedia Foundation.