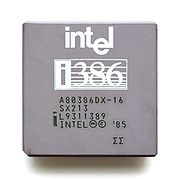

- 80386

-

Diese Variante des weitverbreiteten AMD Am386DX-40 wurde direkt auf die Hauptplatine gelötet.

Diese Variante des weitverbreiteten AMD Am386DX-40 wurde direkt auf die Hauptplatine gelötet.Der 80386 ist eine x86-CPU, die von Intel unter dem Markennamen i386 als Nachfolger des 80286 entwickelt wurde. Der 386er – wie der 80386 häufig auch genannt wird (gesprochen Dreisechsundachtziger)– wurde später von AMD kopiert und als Am386 verkauft, während Chips & Technologies eine kompatible eigene Version entwickelte. IBM lizenzierte den i386SX und entwickelte daraus den verbesserten IBM 386SLC.

Inhaltsverzeichnis

Geschichtliche Bedeutung

Mit dem 80386 vollzog Intel den Wechsel zur 32-Bit-Architektur (IA-32, oft auch i386 genannt), deren Funktionen auch in allen Nachfolgemodellen bis zum Core i7 (Stand 2008) immer noch vorhanden sind und die gleichzeitig anderen Herstellern als Vorlage für eigene Prozessoren diente. Die Register dieser Prozessorfamilie sowie der Adressraum der Architektur sind 32 Bit breit. Auch heute noch wird der 80386 für Steuerungsaufgaben (z. B. Telefonvermittlungsanlagen) eingesetzt.

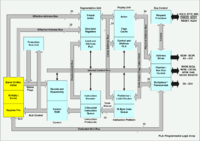

Architektur

Varianten

Eine Variante des 80386 ist der 80386SX. Er besitzt nur einen 16 Bit breiten externen Datenbus und einen 24 Bit breiten Adressbus, behält intern aber die 32-Bit-Mikroarchitektur des 80386 bei. Der 24 Bit breite Adressbus beschränkt den physikalisch adressierbaren Speicher des 386SX zwar auf 16 MB; angesichts eines zu Beginn der 1990er Jahre im Heimbereich üblichen Speicherausbaus von zumeist maximal 4 MB war das aber keine gravierende Einschränkung, zumal viele 386SX-Mainboards einen Speicherausbau von 16 MB auch nicht erlaubten. Aus Sicht des Programmierers besteht praktisch kein Unterschied zwischen dem 386SX und dem „echten“ 80386, der zur Unterscheidung von seinem kleinen Bruder nach dessen Einführung in 80386DX umbenannt wurde. Aufgrund der verringerten Datenbusbreite und niedrigerer verfügbarer Taktfrequenzen erreicht der 386SX gegenüber dem 386DX nur eine deutlich geringere Ausführungsgeschwindigkeit.

Segmente

Der 80386 kann direkt bis zu 4 GB Hauptspeicher adressieren (386SX: 16 MB). Der logische Adressraum beträgt 246 Byte = 64 TB, welcher aber nur theoretisch vollständig nutzbar ist. Der Prozessor verwendet dabei im Protected Mode die segmentierte Speicheradressierung mit 16-bit breiten Selektoren und 32-bit Offsets. Auf Segmentebene gibt es 4 Privilegstufen:

- Ring 0 – für den Betriebssystemkern und Treiber

- Ring 1 – wird selten genutzt

- Ring 2 – für Anwendungsdienste

- Ring 3 – für die Ausführung von normalen Anwendungen

Bei Verwendung eines einzigen Daten- und Code-Segmentes ist der Speicherort linear über den 32-bit Offset ansprechbar, jedoch ohne Speicherschutz auf Segmentebene.

Paging

Zur Verwaltung dient nun eine zusätzliche Ebene welche 4 KB große Speicherseiten (engl. memory pages) verwendet. Die Basisadressen aller Seiten werden in Seitentabellen (engl. page tables) verzeichnet. Diese werden in Seitenverzeichnissen (engl. page directories) zu 1024 Einträgen gespeichert. Ein Adressraum der Größe 4 GB wird folglich in 1024×1024 Seiten zu 4 KB aufgeteilt. So kann die lineare 32-bit Adresse in 3 Bestandteile aufgeteilt werden:

- 12 bit – Offset in der Speicherseite

- 10 bit – Index auf Seitentabelle

- 10 bit – Index auf Seitenverzeichnis

Auf der Seitenebene gibt es zwei Privilegstufen:

- Supervisor-Mode – für Betriebssystem und Treiber (Ring 0, 1 und 2)

- User-Mode – für Anwendungsprogramme (Ring 3)

In Klammern ist die Entsprechung der Segmentprivilegien angegeben.

Register

Er hat acht allgemeine 32-Bit-Register, die zwar teilweise spezielle Verwendungszwecke im Zusammenhang mit verschiedenen Befehlen haben, aber ansonsten frei zum Rechnen und allgemeinen Datenaustausch verwendet werden können:

Die „General-Purpose“-Register des 80386 Abk. Englischer Name Spezielle Verwendung EAX Accumulator spezielle Bedeutung bei Arithmetikbefehlen EBX Base Register keine (Das 16-Bit-Register BX konnte im 16-Bit-Modus zur Index-Adressierung benutzt werden; im 32-Bit-Modus ist dies mit allen „General-Purpose“-Registern möglich.) ECX Count Register spezielle Bedeutung bei Schleifen EDX Data Register spezielle Bedeutung bei Multiplikation, Division und Portadressen für die Assembler-Befehle IN und OUT EBP Base Pointer Zeiger auf temporäre Speicherstellen im Stack (z. B. Stackframe für lokale Variablen etc.) ESP Stack Pointer Zeiger auf die aktuelle Position im Stacksegment; nur eingeschränkt allgemein verwendbar, da dieses Register angibt, wo die Rücksprungadresse von Unterprogrammen und Interrupts gespeichert wird. ESI Source Index Quelle für String-Operationen EDI Destination Index Ziel für String-Operationen Daneben gibt es auch noch weitere Register zur Steuerung des Verhaltens der CPU:

Die Spezialregister des 80386 Abk. Englischer Name Verwendung EIP Instruction Pointer Zeigt auf den nächsten auszuführenden Befehl. Wird durch Sprunganweisungen verändert. EFLAGS Flag Register Die einzelnen Bits besitzen unterschiedliche Bedeutungen und zeigen z. B. Überläufe bei arithmetischen Operationen u. ä. an. CS Code Segment Gibt die Position des Codesegmentes (in dem der aktuell auszuführende Programmcode steht) an. DS Data Segment Gibt die Position des Datensegmentes (in dem die globalen Daten des Programms stehen) an. SS Stack Segment Gibt die Position des Stacksegmentes (in dem der Stack für die lokalen Daten und Rücksprungadressen stehen) an. ES Extra Segment Gibt die Position eines weiteren Datensegmentes (wird z. B. für String-Kopierbefehle verwendet) an. FS und GS Extra Segment 2 und 3 Gibt die Position zweier weiterer Datensegmente an. GDTR Global Descriptor Table Register Gibt die Position der GDT an LDTR Local Descriptor Table Register Gibt die Position der LDT an IDTR Interrupt Descriptor Table Register Gibt die Position der IDT an CR0 – CR3 Control Register 0 … 3 Steuern u. A. das Paging im Protected Mode TR6 – TR7 Test Register 6 … 7 Zum Überprüfen des Translation Lookaside Buffer (TLB). (Es gibt beim 80386 keine Register mit den Namen TR0 bis TR5!) DR0 – DR7 Debug Register 0 … 7 Dienen zum Festlegen von Breakpoints auf Prozessorebene (DR0..DR3) u. a. TR Task Register Segmentselektor des Task Status Segments (TSS) Alle Register, deren Name mit E beginnen, mit Ausnahme von ES, sind auf 32 Bit erweiterte (das E kommt vom englischen extended) Versionen entsprechender 16-Bit-Register der Vorgänger 8086 bis 80286.

Prozessor-Bugs

MUL-Bug

Dieser Fehler tritt nur bei frühen 386-Versionen mit 16 und 20 MHz (A- und B-Steppings) auf, wobei nicht jede einzelne CPU davon betroffen ist. Der Fehler tritt bei der Multiplikation von 32-Bit-Zahlen (MUL als 32-Bit-Befehl) auf und führt zu einem falschen Rechenergebnis, bei Verwendung eines 80387-Koprozessors kann die CPU in einen undefinierten Zustand versetzt werden. Der Fehler wurde erst Anfang 1987 erkannt. Auf Grund des Fehlers sah sich Intel zu einer der ersten großen Rückrufaktionen in der Firmengeschichte veranlasst. Die zurückgelieferten CPUs wurden von Intel geprüft und bei bestandenen Test mit „ΣΣ“ (Doppel-Sigma) gekennzeichnet wieder in Umlauf gebracht. Exemplare, die den Test nicht bestanden, wurden ebenfalls wieder in Umlauf gebracht, allerdings mit der nachträglich aufgebrachten Aufschrift „16 BIT S/W ONLY“, die darauf hinweisen sollte, dass der MUL-Befehl als 32-Bit-Befehl nicht zu verwenden sei.

POPAD-Bug

Dieser Fehler tritt bei allen 386ern auf. Dieser Fehler tritt auf, wenn unmittelbar nach einem 32-Bit-Speicherzugriffsbefehl der Befehl POPAD ausgeführt wird und führt dazu, dass der Inhalt des Registers EAX durch POPAD nicht korrekt aktualisiert wird. Der Linux-Kernel führt beim Booten einen Test durch und gibt bei vorhandenem Fehler die Meldung Checking for popad bug... Buggy. aus, bootet anschließend aber weiter.

Modelle

AMD

Chips & Technologies

IBM

Intel

Desktop:

Embedded:

Mobile:

Siehe auch

- Assemblersprache

- Liste der Mikroprozessoren von Intel

- Liste von Mikroprozessoren

- 386 DX, ein russischer Medienkünstler, der sich nach diesem Prozessortyp benannt hat und ihn bei seinen Auftritten verwendet.

Weblinks

Mikroprozessoren von Intel | Intel-Prozessoren | ModellnummernNon-x86-Prozessoren: 4004 | 4040 | 8008 | 8080 | 8085 | iAPX 432 | i860 | i960 | Itanium | Itanium 2

Bis 4. Generation: 8086 | 8088 | 80186 | 80188 | 80286 | i386 | i486DX | i486DX2 | DX4 | i486GX | i486SL/SL-NM | i486SX | i486SX2

Pentium-Serie: Desktop: Pentium (MMX) | Pentium II | Pentium III | Pentium 4 | Pentium 4 XE | Pentium D | Pentium XE | Pentium Dual-Core

Mobil: Mobile Pentium 4 | Pentium M | Pentium Dual-Core Server: Pentium Pro

Celeron-Serie: Desktop: Celeron (P6) | Celeron (NetBurst) | Celeron D | Celeron (Core) | Celeron Dual-Core Mobil: Mobile Celeron | Celeron M

Core-Serie: Desktop: Core 2 Duo | Core 2 Quad | Core 2 Extreme Mobil: Core Solo | Core Duo | Core 2 Solo | Core 2 Duo | Core 2 Extreme

Nehalem-Serie: Core i5 | Core i7

Xeon-Serie: Server: Xeon (P6) | Xeon (NetBurst) | Xeon (Core)

Wikimedia Foundation.