- Sun SuperSPARC

-

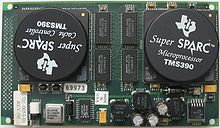

Der SuperSPARC ist ein von Sun Microsystems entworfener superskalarer Mikroprozessor. Da Sun jedoch nicht über die geeigneten Fertigungsstätten verfügte, wurden die Prozessoren in den Hallen von Texas Instruments gefertigt.

Die ersten Prozessoren mit dem Codenamen Viking wurden im Jahr 1991 angekündigt, jedoch begann die Auslieferung der ersten SPARCstation 10 erst im Mai 1992. Im Laufe des Jahres 1994 wurde der leicht verbesserte Nachfolger SuperSPARC II vorgestellt.

Inhaltsverzeichnis

Geschichte

Nachdem der Plattformwechsel zur Sun-4 Serie 1987 gestartet wurde, begann kurz darauf die Entwicklung eines mehrprozessorfähigen Nachfolgers der aktuellen SPARC V7 Generation. Ziel war es, einen modernen superskalaren Prozessor zu entwickeln, der nach Anwendungsanalysen von Sun am effektivsten bei drei Befehlen pro Takt arbeitet, einen integrierten Cache und eine möglichst effektive Pipeline besitzt. Neben den bereits erwähnten Punkten bot dieses Prozessorkonzept, gegenüber dem Vorgänger, außerdem eine integrierte Floating Point Unit und die Anbindung eines optionalen Cache Controllers. Dieser wiederum sollte die Möglichkeit haben, einen großen L2-Cache anzusprechen. Der Produktionsbeginn sollte bereits 1990 erfolgen, wurde aber aufgrund von Schwierigkeiten bei der Herstellung immer wieder verschoben.

Während der MicroSPARC bei Sun das Segment für Uniprozessorsysteme bediente, wurde der SuperSPARC gemäß seiner Entwicklung als Multiprozessor für Workstations und Supercomputer eingesetzt. Der Großteil der gebauten Prozessoren fand Verwendung in der SparcStation 10/20 und in den von anderen Herstellern gefertigten Nachbauten. Erwähnenswert ist außerdem der Einsatz in den leistungsstärksten Servern Sun SparcCenter 2000, Cray CS6400 und Thinking Machines CM-5E mit jeweils bis zu 20, 64 bzw. 128 Prozessoren.

Als Nachfolger des SuperSPARC sollte bereits 1994 der UltraSPARC antreten, jedoch verzögerte sich die Auslieferung der ersten Maschinen bis zum Winter 1995. Die entstandene Lücke konnte der SuperSPARC nicht füllen, da er bei 85 MHz zur Überhitzung in einigen Maschinen neigte und deshalb der Betrieb nur in bestimmten Servern zugelassen war. Um weiterhin mit anderen Systemen konkurrieren zu können, wurde der HyperSPARC angeboten, der bis dahin als SuperSPARC-Konkurrent auf dieser Plattform positioniert war.

Architektur

Der Mikroprozessor basiert auf den Spezifikationen der SPARC V8 Prozessorarchitekur und erbt daher alle Eigenschaften. Das Grundgerüst bildet ein dreifach superskalarer 32-bit-Prozessorkern mit zwei Integer Units (IU) und einer Floating Point Unit (FPU). Die Integer Units verfügen über eine 4-stufige Pipeline und ermöglichen es dem SuperSPARC, bis zu zwei Ganzzahloperationen pro Takt durchzuführen. Dieser hohe Durchsatz wird in realen Situationen aufgrund von Programmverzweigungen und Datenabhängigkeiten nur selten erreicht. Um jedoch die maximale Ausbeute zu erhöhen, wurden die Techniken Branch Prediction und Data Forwarding im Prozessor implementiert.

Die Floating Point Unit besteht aus zwei unabhängigen Pipelines, einem Floating Point Adder (FADDER) für Addition, Subtraktion und Logische Operationen, einem Floating Point Multiplier (MULTIPLIER) für Multiplikationen und einem Floating Point Controller. Jede der beiden Verarbeitungseinheiten ist einer der Pipelines zugeordnet und wird bei Bedarf mit Daten gefüllt. Der Floating Point Controller entnimmt alle Gleitkommabefehle aus der letzten Piplelinestufe der IU, entscheidet Anhand der Art des Befehls welche Ausführunseinheit für die Anweisung zuständig ist und füllt die entsprechende Pipeline.

Wie jeder SPARC verfügt der SuperSPARC über ein großes Registerfeld von 128 Ganzzahl- und 32 Gleitkomma-Registern, die nicht direkt, sondern nur über das entsprechende Registerfenster angesprochen werden können. Daneben existieren noch acht globale Register.

Der SuperSPARC II verbesserte einige Aspekte des Designs. So erhielt die Floating Point Unit eine weitere Einheit, den Floating Point Divide/Square Root (FDS) für Division- und Quadratwurzelberechnungen und somit auch eine dritte Pipeline. Außerdem wurde das Integer-Registerfeld überarbeitet, um die Taktrate leichter zu erhöhen.

Modelle

SuperSPARC (Viking)

- L1-Cache: 20 KB (Daten) + 16 KB (Instruktionen)

- L2-Cache: kein, 1 MB oder 2 MB

- SPARC V8

- MBus/XBus

- Erscheinungsdatum: 1991

- Fertigungstechnik: 0,8 µm BiCMOS

- Transistoranzahl: 3,1 Millionen

- Taktraten: 33-60 MHz

- Modellnummern

- SM20: 1 CPU, kein L2-Cache, 33 MHz Bus: 33 MHz

- SM21: 1 CPU, 1 MB L2-Cache, 33 MHz Bus: 33 MHz

- SM30: 1 CPU, kein L2-Cache, 36 MHz Bus: 36 MHz

- SM40: 1 CPU, kein L2-Cache, 40 MHz Bus: 40 MHz

- SM41: 1 CPU, 1 MB L2-Cache, 40 MHz Bus: 40 MHz

- SM50: 1 CPU, kein L2-Cache, 50 MHz Bus: 50 MHz

- SM51: 1 CPU, 1 MB L2-Cache, 50 MHz Bus: 40 MHz

- SM51-2: 1 CPU, 2 MB L2-Cache, 50 MHz Bus: 40 MHz

- SM52: 2 CPU, 1 MB L2-Cache, 45 MHz Bus: 40 MHz

- SM52X: 2 CPU, 1 MB L2-Cache, 50 MHz Bus: 40 MHz

- SM61: 1 CPU, 1 MB L2-Cache, 60 MHz Bus: 50 MHz

- SM61-2: 1 CPU, 2 MB L2-Cache, 60 MHz Bus: 50 MHz

SuperSPARC II (Voyager)

- L1-Cache: 20 KB (Daten) + 16 KB (Instruktionen)

- L2-Cache: 1 MB oder 2 MB

- SPARC V8

- MBus/XBus

- Erscheinungsdatum: 1994

- Fertigungstechnik: 0,8 µm BiCMOS

- Transistoranzahl: 3,1 Millionen

- Taktraten: 75-90 MHz

- Modellnummern

- SM71: 1 CPU, 1 MB L2-Cache, 75 MHz Bus: 50 MHz

- SM81: 1 CPU, 1 MB L2-Cache, 85 MHz Bus: 50 MHz

- SM81-2: 1 CPU, 2 MB L2-Cache, 85 MHz Bus: 50 MHz

- SM91-2: 1 CPU, 2 MB L2-Cache, 90 MHz Bus: 50 MHz

Quellen

Literatur

- SPARC International Inc.: The SPARC Architecture Manual Version 8, 1991

- Sun Microsystems Computer Corporation: The SuperSPARC Microprocessor - Technical White Paper, 1992

- Sun Microsystems Computer Corporation: The SuperSPARC II Microprocessor - Technical White Paper, 1995

Wikimedia Foundation.