- Front Side Bus

-

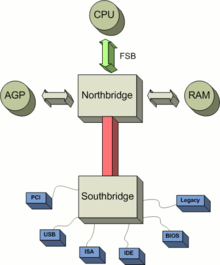

Schema eines Chipsatzes (FSB grün)

Schema eines Chipsatzes (FSB grün)

Front Side Bus (FSB) ist ein Begriff aus der Computertechnik.

Inhaltsverzeichnis

Funktion

FSB ist eine Schnittstelle zwischen dem Hauptprozessor (CPU) und der Northbridge. Über die Northbridge sind der Arbeitsspeicher (RAM) und der AGP-Steckplatz oder der PCI-Express-Steckplatz der Grafikkarte angebunden. Die Southbridge, die über einen Bus mit der Northbridge verbunden ist, kontrolliert die I/O-Schnittstellen wie Festplatten-, USB- oder Netzwerk-Schnittstellen. Der FSB gibt den Takt aller angesprochenen Komponenten vor, der mithilfe von Teilern und Multiplikatoren verändert werden kann (Beispiel: Prozessortakt = FSB × CPU-Multiplikator).

Neuere Prozessoren mit integriertem Speichercontroller (z. B. Athlon 64, Opteron oder Intel Core i7, Intel Xeon) sind nicht mehr über einen klassischen FSB an die Northbridge angebunden, sondern über eine HyperTransport- bzw. QPI-Verbindung. Der Takt von HyperTransport ist dabei über einen Multiplikator und den Referenztakt von 200 MHz festgelegt. Häufig wird dieser Takt fälschlicherweise als „FSB“ bezeichnet. Von dem Referenztakt hängen aber nicht nur der Takt der HyperTransport-Verbindung ab, sondern auch derjenige des Prozessors (Prozessortakt = Referenztakt × CPU-Multiplikator). Probleme wie asynchroner Takt zwischen Hauptspeicher und FSB gehören durch die Integration des Speichercontrollers in den Hauptprozessor der Vergangenheit an.

Als Leistung des Front Side Bus wird in der Regel die Taktfrequenz des Busses angegeben, bei DDR- beziehungsweise QDR-Bussen das entsprechende Vielfache. Die Datenbreite oder maximale Übertragungsrate wird dagegen meist nicht als charakteristisches Merkmal angegeben.

FSB-Varianten

Bei Systemen, die auf Pentium 4, Pentium M oder Intel Core basieren, arbeitet der Front Side Bus im QDR-Verfahren (Quadruple Data Rate = vierfache Datenrate) und überträgt vier Datenpakete pro Taktsignal. Dieses Verfahren wurde von Intels Marketing-Abteilung quadpumped genannt, um diese technische Eigenschaft besser und klangvoller vermitteln zu können. Allerdings entstanden dadurch auch immer wieder falsche Angaben zur Taktfrequenz des FSB: Der FSB dieser Prozessoren läuft auf einer Taktfrequenz von 100 bis 400 MHz („FSB 400“ bis „FSB 1600“), wird jedoch immer wieder gerne – wenn auch falsch – als 400- bis 1600-„MHz“-FSB bezeichnet, was die Wortschöpfung „Marketing-MHz“ hervorgebracht hat.

Ein ähnliches Verfahren beim FSB setzt AMD beim Sockel A oder IBM beim PowerPC G5 ein: Dort läuft der FSB im DDR-Verfahren (Double Data Rate = zweifache Datenrate) und überträgt zwei Datenpakete pro Taktsignal. Auch hier ist oft fälschlicherweise von 200- bis 400-„MHz“-FSB die Rede, obwohl es sich tatsächlich um 100- bis 200-MHz-FSB („FSB 200“ bis „FSB 400“) handelt.

Bei älteren Computersystemen wie Sockel 7, Sockel 370 oder älter läuft der FSB im SDR-Verfahren (Single Data Rate = einfache Datenrate) und überträgt ein Datenpaket pro Taktsignal. Eine Angabe wie „FSB 100“ bezeichnet dort auch immer die Taktfrequenz des FSB in MHz (hier 100 MHz).

übliche Taktfrequenzen und Bezeichnungen

Taktfrequenz Bezeichnung DDR-FSB („Doublepumped“) 100 MHz FSB 200 133 MHz FSB 266 166 MHz FSB 333 200 MHz FSB 400 QDR-FSB („Quadpumped“) 100 MHz FSB 400 133 MHz FSB 533 166 MHz FSB 667 200 MHz FSB 800 266 MHz FSB 1066 333 MHz FSB 1333 400 MHz FSB 1600 Bandbreite am Beispiel des Serie-4-Chipsatzes von Intel

Der FSB der Intel-Serie-4-Chipsatzfamilie für Intel-Core-2-Prozessoren und Sockel LGA775 besteht aus 33 Adressleitungen, 64 Datenleitungen und Steuer- und Taktleitungen. Die Adressleitungen werden im DDR-Verfahren betrieben (zwei Transfer pro Takt), bei 33 Adressleitungen kann so mit jedem Takt eine 64 Bit umfassende Adresse übertragen werden. Die Datenleitungen laufen im QDR-Verfahren (vier Transfer pro Takt). Damit lassen sich je Takt Daten im Umfang von 4 x 64 = 256 Bit bzw. 256/8 = 32 Byte übertragen. Die mit dem Chipsatz verwendeten Prozessoren transportieren als kleinste Speichereinheit eine Cache Line (64 Byte) vom und zum RAM, das benötigt zwei Takte. Der Chipsatz unterstützt einen FSB-Takt von 200, 266 oder 333 MHz, multipliziert mit 32 Byte ergibt das auf dem Datenbus eine Bandbreite von 6,4 oder 8,5 oder maximal 10,6 Gigabyte/s .[1]

Siehe auch

Einzelnachweise

- ↑ Intel® 4 Series Chipset Family Datasheet, März 2010, Seite 525f http://www.intel.com/Products/Desktop/Chipsets/G45/G45-technicaldocuments.htm

Kategorien:- Inter-Chip Bus

- Chipsatz

Wikimedia Foundation.