- Bus (Datenverarbeitung)

-

Ein Bus ist ein System zur Datenübertragung zwischen mehreren Teilnehmern über einen gemeinsamen Übertragungsweg, bei dem die Teilnehmer nicht an der Datenübertragung zwischen anderen Teilnehmern beteiligt sind.[1]

Bussysteme finden Anwendung insbesondere innerhalb von Computern und zur Verbindung von Computern mit Peripheriegeräten, aber auch in der Ansteuerung von Maschinen (Feldbusse) sowie immer häufiger in Automobilen zur Verbindung der einzelnen elektronischen Systemkomponenten eines Fahrzeugs. Auch in der Gebäudetechnik werden Busse verwendet, z. B. der Europäische Installationsbus (EIB).

Inhaltsverzeichnis

Grundbegriffe

Frühere Busse waren tatsächlich nur parallele Stromschienen mit mehreren Anschlüssen. Aus dieser Zeit (ab 1898) stammen die Bezeichnungen omnibus bar und abgekürzt bus bar für solche Sammelschienen (power rail). Die Bezeichnung wurde für Daten-Sammelleitungen (Datenbusse) übernommen, die Informationen an die angeschlossenen Teilnehmer weitergeben.

Die an einem Bus angeschlossenen Komponenten werden auch als Knoten oder Busteilnehmer bezeichnet. Knoten, die selbständig auf den Bus zugreifen dürfen (im Sinne von schreiben bzw. senden), bezeichnet man als aktive Knoten oder Master, andernfalls heißen sie passive Knoten oder Slave. Ein Bus, der mehrere Master-Knoten erlaubt, heißt Multimaster-Bus. Bei einem Multimaster-Bus ist eine zentrale oder dezentrale Busvermittlung notwendig, die gewährleistet, dass zu jedem Zeitpunkt jeweils nur ein Master die Bus-Herrschaft besitzt. Dies ist notwendig, da durch gleichzeitige schreibende Zugriffe auf den Bus nicht nur Daten verloren gehen können, sondern auch die Hardware beschädigt werden könnte. Bei einer zentralen Busvermittlung wird der Buszugriff von einer speziellen Komponente gesteuert, die Bus-Arbiter genannt wird. Derjenige Knoten, der einen Zugriff auf den Bus initiiert, heißt Initiator, das Ziel eines solchen (lesenden oder schreibenden) Zugriffes heißt Target.

Je nach Verwendungsart unterscheidet man Systembusse, Speicherbusse, Peripheriebusse und Ein-/Ausgabebusse. Darüber hinaus lassen sich grundsätzlich parallele von seriellen Bussen unterscheiden.

Bus-Strukturen

Topologie und Terminierung

Ob etwas funktionell ein Bus ist, hängt nicht von der physischen Topologie ab.[1] Da auf Bussen oft sehr hochfrequente elektrische Signale übertragen werden, treten an Verzweigungen Reflexionen auf, was zu Auslöschung der Signale durch Interferenz an bestimmten Stellen und damit zur Fehlfunktion des gesamten Systems führt. Deshalb ist die Linien-Topologie signaltechnisch überlegen und am häufigsten anzutreffen (Beispiel SCSI). Reflexionen an den Leitungsenden werden durch Terminierung verhindert. Terminierung durch einen Abschlusswiderstand verursacht eine hohe Verlustleistung, ein RC-Glied schwankenden Ruhepegel. Aufwendiger ist die aktive Terminierung, die den Ruhepegel durch einen Spannungsregler vorgibt.

Multiplexing

Da Adress- und Datenbusse auf einer Leiterplatte eine große Anzahl gleichartiger Leiterbahnen benötigen, verbraucht dies einerseits viel Platz und benötigt entsprechend viele Pins an den Bausteinen, andererseits kann das auch elektrische Probleme wie Übersprechen vergrößern. Deshalb gibt es als eine Lösung den Ansatz, diese Anzahl zu halbieren, indem man in einer Busphase die eine Hälfte und in einer anderen die andere Hälfte der Signale über dieselben Leitungen schickt (Multiplexbus). Ein zusätzlicher Steuerpin muss dann diese Busphasen kennzeichnen. Es handelt sich also um ein Zeitmultiplex-Verfahren. Das wurde in der Praxis z. B. beim Adressbus des 8080-Prozessors so gemacht, und bei dynamischen RAMs (DRAMs) führt das zu den RAS- und CAS-Zyklen.

Bus als Teil des Computers

In der Computerarchitektur ist ein Bus ein Untersystem, das Daten oder Energie zwischen Computerbestandteilen innerhalb eines Computers oder zwischen verschiedenen Computern überträgt. Anders als bei einem Anschluss, bei dem ein Gerät mit einem anderen über eine oder mehrere Leitungen verbunden ist (Point-to-Point-Verbindung), kann ein Bus mehrere Peripheriegeräte über den gleichen Satz von Leitungen miteinander verbinden.

Moderne Computerbusse können sowohl parallel, als auch bit-seriell verwendet werden. Während bei der eigentlichen Netz-Topologie der klassischen Bus-Leitung alle Teilnehmer nebeneinander am Bus hängen, können durch geeignete Kontaktierungen Knoten in einer kettenförmigen Anordnung hintereinander geschaltet werden. Neben der Netzwerktopologie auf der physikalischen Ebene kann ein busähnliches Verhalten auch durch entsprechende Implementierungen nachgebildet werden (vgl. OSI-Modell mit höheren Übertragungsebenen).

Die meisten Computer haben interne und externe Busse. Ein interner Bus schließt alle internen Bestandteile eines Computers an die Hauptplatine an (und folglich die CPU und den internen Speicher). Ein solcher interner Bus wird auch als lokaler Bus bezeichnet, weil er dafür gedacht ist, mit im Computer selbst vorhandenen Geräten zu verbinden, und nicht mit solchen in anderen Computern oder mit externen. Ein externer Bus schließt demgemäß externe Peripherie an die Hauptplatine an.

Adressierungsverfahren

Ein Bussystem ist immer so organisiert, dass zu einem bestimmten Zeitpunkt nur ein einzelner Knoten Daten auf den Bus ausgibt. In den allermeisten Fällen sollen die Daten zu einem bestimmten anderen Knoten transportiert und von diesem weiterverarbeitet werden (Nur in seltenen Fällen verwerten mehrere Empfangsknoten gleichzeitig die gesendeten Daten, beispielsweise bei den CAN-Bussen eines Automobils). Zur Identifizierung des Zielknotens wird eine Adressierung vorgenommen, oft über den eigens dafür eingerichteten Adressbus.

Busse unterscheiden sich in der Art, wie einzelne Knoten adressiert werden. Sowohl für parallele als auch für serielle Busse gibt es eine Reihe typischer Verfahren.

Adressierung in Parallelbussen

Ein einfaches Adressierungsschema sieht wie folgt aus: Lediglich eine einzige Komponente ist ein Busmaster (in der Regel ist dies der Prozessor), alle anderen sind passiv. Legt nun der Master eine Adresse auf dem Adressbus an, so wird diese von einem zentralen Adressdekoder dekodiert. Dieser ermittelt die adressierte Komponente und teilt dieser über eine Select-Leitung mit, dass sie die adressierte Komponente ist. Die eigentlichen Daten werden anschließend separat über den Datenbus gesendet.

Eine Modifikation dieses Schemas ergibt sich, wenn kein zentraler Adressdekoder verwendet wird, sondern jede angeschlossene Komponente über einen eigenen Adressdekoder verfügt. Die einzelnen Adressdekoder entscheiden dann anhand der angelegten Adresse unabhängig voneinander, ob ihre Komponente die gemeinte ist oder nicht.

Ein anderes Prinzip arbeitet ganz ohne Adressleitung. Der Bus besteht ausschließlich aus Datenleitungen, welche direkt zu der jeweils ausgewählten Komponente laufen. An derartigen Bussen können folglich nur so viele Komponenten angeschlossen werden, wie es parallele Datenleitungen im Bus gibt. Ein prominentes Beispiel für dieses Adressierungsverfahren liefert der SCSI-Bus.

Die beschriebenen Verfahren können auch miteinander kombiniert werden. Darüber hinaus ist zu beachten, dass reale Bustopologien in der Regel weit komplexer sind als die hier angenommenen. So werden in einem Rechensystem in der Regel verschiedene Bustypen zu einer Bushierarchie miteinander verbunden, die sich in der Art der Adressierung unterscheiden und über Brücken miteinander gekoppelt sind. Derartige Brücken sind in der Lage die Adressierung von einem Busprotokoll in das andere zu übersetzen. Auch spezielle Adressierungs-Aspekte von Multimaster-Bussen wurden hier nicht berücksichtigt.

Adressierung in seriellen Bussen

Die auf seriellen Bussen übertragenen Daten lassen sich als Datenpakete (oder auch Telegramme) betrachten, die in mehrere Felder unterteilt sind. Ein typisches Datenpaket weist neben der Sender-Adresse auch die Empfänger-Adresse des Pakets auf. Angeschlossene Komponenten betrachten das Empfängerfeld und entscheiden dann, ob sie das Paket verarbeiten oder verwerfen.

Auch serielle Busse können natürlich als direkte Datenleitungen von Komponente zu Komponente konzipiert sein. In diesem Fall sind die Sender- und Empfänger-Felder überflüssig.

Busmastering

Busmastering bedeutet, dass der Prozessor eines Computersystems zeitweilig die Kontrolle über den Bus an eine Adapterkarte, den so genannten Busmaster, abgibt. Dieser Busmaster adressiert in der Folge selbständig Speicher und IO-Bereiche zum Zweck des Datentransfers. Der Busmaster operiert also als eine Art Bridge bzw. wie eine eigenständige CPU. Während also solch ein sekundärer Prozessor den peripheren Bus beherrscht, ist die CPU meist in der Lage andere Arbeiten im System auszuführen, sofern die dafür nötigen Ressourcen im Zugriff sind. Meist ist der Bus zum Speicher hin noch teilweise nutzbar, es herrscht also Time-Sharing. Dies macht sich insbesondere bei modernen Multitasking-Betriebssystemen durchaus positiv in der Reaktionsfähigkeit bemerkbar, wobei die Busmaster-Aktivität oftmals über ein Interrupt-Signal mit dem Betriebssystem verkoppelt ist. Die Adapterkarte hat dabei den Sinn, bestimmte Aufgaben asynchron zu anderen Tasks zu bedienen.

Beschränkt man sich beim Bus-Mastering nicht auf Busse an der CPU eines Computers, gibt es im Bereich der Rechnernetze noch weitere Methoden zum Bus-Arbiting:

- Beim Token-Passing hält der jeweils aktive Busmaster ein so genanntes Token, das nichts anderes als eine Merkvariable (Flag) ist. Hat er seine Sendung abgeschlossen, reicht er dieses Token an einen bestimmten Nachbarn auf dem Bus (im Rechnernetz) weiter. Das wird vor allem in Ringbussen angewandt. Wenn man es physikalisch nicht mit einem Ringbus zu tun hat, ist es Software-Angelegenheit, die potenziellen Busteilnehmer in eine wohldefinierte und allen bekannte Reihenfolge zu bringen.

- Andere Busse (Beispiel: CAN oder Ethernet) sind von vornherein darauf vorbereitet, dass es zu Kollisionen mehrerer Teilnehmer kommen kann, die gleichzeitig zu senden versuchen. Es ist dann deren zusätzliche Aufgabe, solche Kollisionen zu erkennen (collision detection) und sinnvoll zu reagieren. Es gehört zur Definition des jeweiligen Busses oder Rechnernetzes, letztere Strategie festzulegen. Es ist offensichtlich, dass so eine Methode auch für drahtlose Funkverbindungen anwendbar ist, entsprechend wird es auch eingesetzt.

Geschichtliche Entwicklung

Erste Generation

Speicher und andere Geräte wurden am Bus an den gleichen Adressen und Datenstiften angebracht, die die CPU selbst benutzt, und zwar durch parallelen Anschluss. Die Kommunikation wurde durch die CPU gesteuert, die die Daten von den Geräten und die Blöcke aus dem Speicher liest. Alles wurde dabei durch einen zentralen Zeitgeber getaktet, der die Arbeitsgeschwindigkeit der CPU steuerte. Angeschlossene Geräte zeigten der CPU, dass sie Daten senden oder empfangen wollen, indem sie auf anderen CPU-Stiften ein Signal sendeten, was gewöhnlich durch eine Form von Interrupt geschah. Zum Beispiel hat ein Laufwerkscontroller (siehe Controller) der CPU signalisiert, dass neue Daten bereit waren gelesen zu werden, worauf die CPU die Daten verschob, indem sie den Speicher an dem Anschluss las, der dem Laufwerk entsprach. Fast alle frühen Computer wurden auf diese Weise zusammengesetzt, beginnend mit dem S-100-Bus im Altair und bis hin zum IBM-PC in den 1980ern.

Diese „erste Generation“ von Bussystemen litt jedoch unter dem gravierenden Nachteil, dass alles auf dem Bus mit der gleichen Geschwindigkeit arbeitet und alle Geräte sich einen einzelnen Taktgeber teilen mussten. Die Arbeitsgeschwindigkeit der CPU zu erhöhen war nicht einfach, weil man die Geschwindigkeit aller angeschlossenen Geräte ebenfalls steigern musste. Dies führte zu der seltsamen Situation, dass sehr schnelle CPUs gedrosselt werden mussten, um mit anderen Geräten im Computer kommunizieren zu können. Ein anderes Problem war, dass die CPU für alle Operationen benötigt wurde, und so, wenn sie mit anderen Aufgaben beschäftigt war, der reale Datendurchsatz des Busses drastisch darunter zu leiden hatte. Ein anderes praktisches Problem war, dass diese frühen Bussysteme schwierig zusammenzustellen waren, da sie viele Jumper erforderten, um die verschiedenen Betriebsparameter einzustellen.

Zweite Generation

Bussysteme der „zweiten Generation“ wie NuBus waren auf die Lösung einiger dieser Probleme gerichtet. Sie teilten den Computer gewöhnlich in zwei „Welten“, die CPU und den Speicher auf der einen Seite und die anzuschließenden Geräte auf der anderen, mit einem Buscontroller dazwischen. Dies erlaubte es, die Geschwindigkeit der CPU zu erhöhen, ohne den Bus zu beeinflussen. Dadurch wurde auch viel von der Belastung für das Verschieben der Daten aus der CPU heraus und in die Karten und den Controller verringert, weil Geräte über den Bus ohne Einschaltung der CPU miteinander sprechen konnten. Dieses führte zu viel besserer tatsächlicher Leistung in der Praxis, erforderte aber auch eine viel höhere Komplexität der im Computer installierten Geräte. Weiter gingen diese Bussysteme das Geschwindigkeitsproblem an, indem sie einfach einen größeren Datentransportweg wählten, und so von den 8-bit parallelen Bussen der ersten Generation zu 16 oder 32-bit in der zweiten übergingen. Eine weitere Verbesserung bestand darin, dass Softwareeinstellungen hinzugefügt wurden, die die Zahl der Jumper reduzierten oder diese ersetzten.

Gleichwohl hatten die neueren Systeme eine negative Eigenschaft, die sie mit ihren früheren Vettern teilten: alles, was am Bus hing (außer der CPU), musste mit der gleichen Geschwindigkeit arbeiten. Da die CPU jetzt isoliert war und man ihre Geschwindigkeit ohne Probleme erhöhen könnte, stieg die Arbeitsgeschwindigkeit der CPUs und des Speichers fortlaufend viel schneller an, als die der Bussysteme, mit denen sie zusammenarbeiteten. Das Resultat war, dass die Busgeschwindigkeiten jetzt sehr viel langsamer waren, als für ein modernes System nötig, und die Maschinen hungerten nach Daten, weil sie viel schneller arbeiteten, als Daten hin und her transportiert werden konnten. Ein besonders typisches Beispiel für dieses Problem war, dass Videokarten sogar den neueren Bussystemen wie PCI schnell davonliefen. So wich man für Grafikkarten vom Bus-Konzept ab und führte einen exklusiven, deutlich schnelleren Anschluss (Port) für die Grafikkarte ein, den Accelerated Graphics Port (AGP). Der nächste Schritt und Stand der Technik Ende 2005 in dieser Entwicklung ist PEG, PCI-Express for Graphics mit 16 Lanes.

Während dieser Periode fing auch eine zunehmende Anzahl von externen Geräten an, ihre eigenen Bussysteme einzusetzen. Als die Laufwerke zuerst eingeführt wurden, hat man sie mit einer Einsteckkarte an den Bus angeschlossen. Das ist der Grund, warum Computer so viele mit dem Bus verbundene Steckplätze (Slots) haben. In den 1980er und 1990er wurden deswegen neue Systeme wie SCSI und ATA eingeführt, und so blieben die meisten Slots in den modernen Systemen leer. Heute gibt es in einem typischen PC an die fünf unterschiedlichen Bussysteme, um die verschiedenen Geräte zu betreiben.

Später ging man dazu über, das Konzept des lokalen Busses im Vergleich zum externen Bus zu bevorzugen. Ersteres bezieht sich auf Bussysteme, die entworfen wurden, um mit internen Geräten, wie Grafikkarten zu arbeiten, letzteres um externe Geräte wie Scanner anzuschließen. Diese Definition war immer ungenau: IDE ist der Verwendungsart nach ein externer Bus; er wird aber fast immer innerhalb des Computers zu finden sein.

Dritte Generation

Busse der „dritten Generation“ sind jetzt im Kommen, einschließlich HyperTransport und InfiniBand. Sie haben gewöhnlich die Eigenschaft, dass sie mit sehr hohen Geschwindigkeiten laufen, die benötigt werden, um Speicher und Videokarten zu unterstützen, während auch niedrigere Geschwindigkeiten möglich sind, um die Kommunikation mit langsameren Geräten, wie Laufwerken zu unterstützen. Sie sind auch sehr flexibel, was ihre physikalischen Anschlüsse betrifft und lassen sich sowohl als interne Busse verwenden, als auch, um verschiedene Rechner miteinander zu verbinden.

Dieses kann zu komplizierten Problemen führen, wenn es darum geht, unterschiedliche Anfragen zu bedienen, was dazu führt, dass die Software im Vergleich zum eigentlichen Hardwaredesign in den Vordergrund rückt. Im Allgemeinen neigen die Busse der dritten Generation dazu, mehr wie ein Netzwerk als wie ein Bus (im traditionellen Verständnis) auszusehen, mit mehr Bedarf an Protokollinformationen als bei früheren Systemen, und der Möglichkeit, dass verschiedene Geräte den Bus gleichzeitig benutzen können.

Bussysteme

Datenbus

Ein Datenbus überträgt Daten zwischen Computerbestandteilen innerhalb eines Computers oder zwischen verschiedenen Computern. Anders als bei einem Anschluss, bei dem ein Gerät mit einem anderen Gerät über eine oder mehrere Leitungen verbunden ist, kann ein Bus mehrere Peripheriegeräte über den gleichen Satz von Leitungen miteinander verbinden. Im Gegensatz zum Adressbus oder Steuerbus ist der Datenbus bidirektional (wenn man vom Adressbus bei DMA-Betrieb absieht).

Die Bezeichnungen 4-Bit-, 8-Bit-, 16-Bit-, 32-Bit- oder 64-Bit-CPU bezeichnen in der Regel die Breite des internen Datenpfades einer solchen CPU. Zumeist ist der interne Datenpfad genauso breit wie der externe Datenbus. Eine Ausnahme ist beispielsweise die Intel-CPU i8088. Hier ist der interne Datenpfad 16 Bit breit, während der externe Datenbus lediglich 8 Bit breit ist. Auf Grafikkarten finden sich auch noch höhere Busbreiten, um die Verarbeitungsgeschwindigkeit zu steigern.

Die Bezeichnung als Datenbus wird in mehrfachem Zusammenhang verwendet:

- mit Betonung auf Daten: zur Abgrenzung gegenüber gemeinsamen Anschlüssen, wie der Stromversorgung

- mit Betonung auf Bus: zur Unterscheidung der Topologie, wie z. B. direkten Punkt-zu-Punkt-Verbindungen

- bei parallelen Bussen: zur Unterscheidung von Adress- oder Steuerleitungen

Adressbus

Ein Adressbus ist im Gegensatz zum Datenbus ein Bus, der nur Speicheradressen überträgt. Die Busbreite, also die Anzahl der Verbindungsleitungen, bestimmt dabei, wie viel Speicher direkt adressiert werden kann. Wenn ein Adressbus n Adressleitungen hat, können 2n Speicherstellen direkt adressiert werden. Bei einem System mit 32 Adressleitungen können also 232 = 4.294.967.296 Byte (eine Speicherzelle = 8 Bit) = 4 GiByte angesprochen werden. Bei einem 64-Bit-System können sogar 264 = 18.446.744.073.709.551.616 Byte = 16 Exbibyte (EiB) angesprochen werden. In der Regel ist der Adressbus physisch nicht in dieser Breite ausgeführt (s. o. bei Multiplexing). Die Angabe 64-Bit-System bezieht sich eher auf die Breite des Datenbusses. Allerdings kann ein 64-Bit-Datum als Adresse einer anderen Speicherstelle aufgefasst werden (indirekte Adressierung).

Dieser Bus ist unidirektional und wird vom jeweiligen Busmaster (s. a. oben) angesteuert. Letzterer ist meistens die CPU, aber vor allem DMA-fähige Bausteine können diesen Bus auch übernehmen, wenn sie aktiv werden. Typische Größen für den Adressbus sind 8, 20 (beim Intel 8088), 24 (beim Nachfolger Intel 80286), 32 (etwa Intel 80486), 36 (Pentium 2 bis Pentium 4), 40 (Athlon), 44 (Itanium) und 64 Bit.

Steuerbus (Kontrollbus)

Der Steuerbus (unidirektional) ist ein Teil des Bussystems (bidirektional), welcher die Steuerung (engl. control) des Bussystems bewerkstelligt. Hierzu zählen unter anderem die Leitungen für die Lese-/Schreib-Steuerung (Richtung auf dem Datenbus), Interrupt-Steuerung, Buszugriffssteuerung, der Taktung (falls ein Bustakt erforderlich ist), Reset- und Statusleitungen. Welche der Leitungen in einem Bus eingesetzt sind, ist von der Art und Struktur des Busses abhängig. In Multi-Master-Systemen, in denen mehr als ein Subsystem die Buskontrolle übernehmen kann, ist ein Arbiter als Entscheidungsinstanz erforderlich.

CPU-interner Bus

Der interne CPU-Bus (engl.: internal CPU bus) dient zur Kommunikation der internen Einheiten des Prozessors (zwischen Leitwerk, Rechenwerk und deren Registern), gegebenenfalls auch mit dem L1-Cache. (aus Hansen Neumann Wirtschaftsinformatik I)

CPU-externer Bus

Der externe CPU-Bus (engl.: external CPU bus) verbindet Prozessor(en), (L2-)Cache, Arbeitsspeicher und Peripheriebus-Schnittstelle, auch Front Side Bus (FSB) genannt, oder alternativ nur mit dem Chipsatz (oder dessen Northbridge), wo jene externen Elemente angeschlossen sind.

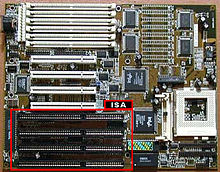

Rechner-interne Busse

Diese Busse verbinden Komponenten innerhalb eines Rechners, also zum Beispiel die CPU mit der Grafikkarte und mit diversen Ein-/Ausgabe-Komponenten.

Rechner-externe Busse

Diese Busse verbinden den Rechner mit externen Peripheriegeräten. Es sind hier nur solche Schnittstellen aufgeführt, die wirklich Bus-Charakter aufweisen, also den Anschluss von mehreren externen Geräten gleichzeitig erlauben.

Siehe auch

Weblinks

Commons: Computerbusse – Sammlung von Bildern, Videos und Audiodateien

Commons: Computerbusse – Sammlung von Bildern, Videos und AudiodateienBelege

- ↑ a b IEC 60050 - International Electrotechnical Vocabulary - Details for IEV number 351-32-10. International Electrotechnical Commission. Abgerufen am 25. Juni 2009.

Wikimedia Foundation.