- High-Level-Logic

-

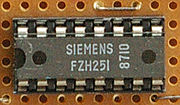

Langsame störsichere Logik (Abk. LSL, engl. Low-Speed Logic), auch unter der Bezeichnung High-Level Logic (HLL) bekannt, ist eine veraltete elektronische Schaltungstechnik (Logikfamilie) für logische Schaltungen (Gatter).

LSL-Schaltungen wurden aus DTL-Schaltungen entwickelt. Durch die Erhöhung der Versorgungsspannung auf 15 Volt wurde die Störsicherheit durch einen höheren Signalabstand zwischen Low-Pegel und High-Pegel erhöht, aber andere Eigenschaften, wie die Signalgeschwindigkeit treten dabei in den Hintergrund. Mit Hilfe einer Z-Diode wird die Eingangsumschaltschwelle auf ca. 6 Volt angehoben.

LSL-Schaltungen sind relativ langsam (Signallaufzeit ca. 200ns) und wurden vor allem in den 1970er und 1980er Jahren eingesetzt. Ein typischer Schaltkreis dieser Logik ist der SAA1029 bzw. der in der DDR nachgebaute Typ D410.

Aufbau

Die nebenstehende Abbildung zeigt ein dimensioniertes LSL-NAND-Gatter mit einer Betriebsspannung von 12V – welche in realen Anwendungen häufiger vorkommt als 15V – und einem Störabstand von etwa 5V. Zur Erhöhung der Ausgangsbelastbarkeit (Fan-Out) wird am Ausgang eine Gegentaktendstufe vorgesehen. Durch die Verwendung langsamer Transistoren und einem außen anschaltbaren Kondensator kann die dynamische Störsicherheit noch weiter gesteigert werden, da sich der Kondensator nur langsam umlädt und so kurzzeitig auftretende Störspannungen unterdrückt, auch wenn diese Störspannungen größer sind als der vorgesehene Störabstand. Die Schaltzeiten werden hierdurch jedoch erheblich verlängert.

Siehe auch

- Widerstands-Transistor-Logik (RTL)

- Diode-Transistor-Logik (DTL)

- Transistor-Transistor-Logik (TTL)

- Emittergekoppelte Logik (ECL)

- Komplementäre MOS-Logik (CMOS)

Wikimedia Foundation.