- KME U80701

-

Der U80701 war der erste in der Deutschen Demokratischen Republik (DDR) hergestellte 32-Bit-Prozessor. Die Entwicklung erfolgte, um die 1989 führende Rechnerlinie von Digital Equipment Corporation, speziell der microVAX II verfügbar zu machen. Demnach wurde der U80701 nach Vorlage der microVAX II (CPU 78032 oder DC333) entwickelt, am 14. August 1989 offiziell vorgestellt und gehörte zum U80700-Prozessorsystem. Er sollte im Robotron Kleinrechner K1820 verwendet werden. Von diesem System wurden wahrscheinlich 10 Muster gebaut. Der Prozessor U80701 wurde nicht mehr in Serienproduktion gefertigt.

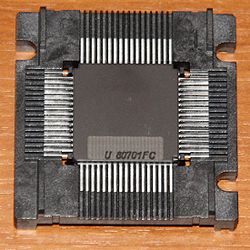

Die CPU war in einem 68-poligen FlatPack-Plastgehäuse untergebracht und konnte bis zu 16 MB physikalischen sowie bis zu 4 Gigabyte virtuellen Speicher adressieren und unterstützte den Protected Modus. Vorhanden war auch ein 512 Byte seitenorientierter Schutzmechanismus.

Die Programmierung erfolgte über 175 Maschinenbefehle, 16 32-Bit-breite allgemeine sowie 20 Prozessor- beziehungsweise interne Register. Die CPU besaß einen 62,4 KB großen ROM mit integriertem 8-Byte Prefetch-Stack. Das ROM enthielt ein Programm zur Ablaufsteuerung. Adress- und Datenbus belegten dieselben Pins, deswegen wurde hier das Multiplexverfahren verwendet. Des Weiteren war es möglich, die CPU durch eine zusätzliche Gleitkommaeinheit zu erweitern.

Zum U80700-Prozessorsystem gehörten folgende Schaltkreise:

- U80701: Hauptprozessor (CPU)

- U80703: Gleitkommaprozessor (FPU)

- U80707: DIGITAL Link asynchronous receiver/transmitter (DLART)

- U80709: CPU-Interface-Gate-Array (CIGA)

- U80711: Bus-Interface-Gate-Array (BIGA)

Daten

Hersteller: VEB Mikroelektronik „Karl Marx“ Erfurt Bezeichnung: U 80701 FC Adressbus: 32 Bit intern/extern Datenbus: 32 Bit intern/extern Entwicklungsbeginn: 1986 nicht funktionierende Muster: 1988 erste funktionsfähige Muster: 1989 Technologie: nSG (NMOS Silizium-Gate) Transistoranzahl: zirka 130.000 Chipfläche: 85 mm² Taktfrequenz: effektiv 5 MHz (abgeleitet aus 40 Mhz) Verarbeitungsgeschwindigkeit K 1820: 0,9 MIPS MMU: integriert Gehäuse: PLCC68 laut Quelle #3, auch CLCC68 bekannt (s. Fotos) Anschlüsse

Bezeichnung Ein-/Ausgang Beschreibung CLK1 Eingang Eingangstakt CLK0 Ausgang Taktausgabe der Normalfrequenz RESET# Eingang RESET der CPU BM0..BM3 Ausgänge Byte-Maske DAL0..DAL31 Ein-/Ausgänge gemultiplexter Daten-/Adressbus AS# Ausgang, Tristate Adress strobe DS# Ausgang, Tristate Data strobe DBE# Ausgang, Tristate Data buffer enable WR# Ausgang, Tristate Write EPS# Ausgang External processor strobe CS0, CS1 Ausgänge, Tristate Bus cycle status CS2 Ein-/Ausgang, Tristate Bus cycle status RDY# Eingang Ready ERR# Eingang Error DMR# Eingang DMA request DMG# Ausgang DMA grant HALT# Eingang Halt-Interrupt-Anforderung INTTIM# Eingang Timer-Interrupt-Anforderung PWRFL# Eingang Power-Fail-Interrupt-Anforderung IRQ0#..IRQ3# Eingänge Interrupt-Anforderung für Standard-I/O-Interrupts TEST Eingang Testeingang für Bauelemente-Hersteller UCCX --- Betriebsspannung zur Versorgung der Pinlogik des Daten-/Adressbusses USSX --- Bezugspotential für UCCX UCCI --- Betriebsspannung für Schaltkreislogik USSI --- Bezugspotential für UCCI UBB --- Bulkspannung, intern generiert Quellen

- Funkamateur 10/89, S. 473 (Bild)

- Computerwoche Nr. 41, 6. Oktober 1989

- Datenbuch Mikroelektronik Gesamtübersicht: Info-Verlag electronic (S. 234 - 236)

- Dieter Walter: Geschichte des VEB Robotron-Elektronik Dresden (S.40); PDF-Datei 1,1 MB

- Autorenkollektiv: Technisches Handbuch ZVE KAC20. VEB Robotron-Elektronik Dresden, Dezember 1989

Weblinks

Wikimedia Foundation.