- Cell Chip

-

Cell ist der Name für eine Prozessorserie, die von IBM gemeinsam mit Sony und Toshiba entwickelt wurde. Die Prozessoren zeichnen sich durch die Nutzung eines 64-Bit-PowerPC-Kernes, einer Pipeline-Architektur, Unterstützung für Simultaneous Multithreading und dem Einsatz einer Multicore-Architektur aus, wodurch sie für paralleles Rechnen prädestiniert sind.

Inhaltsverzeichnis

Aufbau

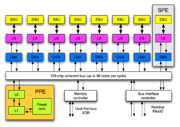

Das Grundkonzept der Cell-Prozessoren sieht acht Synergistic Processing Elements (SPE) und ein PowerPC Processing Element (PPE) vor. Jedes SPE besteht aus einer Recheneinheit (ALU) mit vierfachem SIMD, bezeichnet als Synergistic Processing Unit (SPU). Diese verfügt über 128 Register, die jeweils 128 Bit groß sind. Zum SPE gehört weiterhin ein Memory Flow Controller (MFC), der DMA-Übertragungen zum Hauptspeicher oder zu anderen SPEs steuert, sowie ein eigener lokaler Speicher von 256 KB, der jedoch nicht durch einen Cache unterstützt wird.

Der Steuerprozessor (PPE) basiert auf der 64-Bit-PowerPC-Architektur von IBM, dessen Pipeline aber im Vergleich zu üblichen PowerPC-Prozessoren in order arbeitet[1]. Da er zwei Threads gleichzeitig abarbeiten kann, entstehen bei entsprechend eingerichteten Programmen die üblichen In-Order-Nachteile durch blockierte Pipelines in geringerem Maße. Dem PPE stehen 512 KB L2-Cache zur Verfügung. Insgesamt verfügt die CPU also über 2,5 MB internen Speicher.

Die einzelnen Prozessorkerne sind über einen Element Interface Bus (EIB) gekoppelt, der Daten mit bis zu 96 Byte pro CPU-Takt übertragen kann. Sowohl das PPE als auch die SPEs können pro CPU-Takt mit 8 Bytes auf den EIB zugreifen. Der EIB ist dabei als Ringbus (4 × 128 Bit) realisiert und wird mit halbem CPU-Takt getaktet. Der Zugriff auf den Hauptspeicher erfolgt über einen Memory Interface Controller (MIC)[2].

Der erste Cell-Prozessor wurde in 90 nm Strukturgröße im SOI-Verfahren gefertigt, dabei erreichte das Die eine Fläche von rund 221 mm²[3]. Ab März 2007 stellte IBM den Prozessor in 65-nm-Verfahren her, was zu einer kleineren Die-Fläche und somit zu geringeren Fertigungskosten führte[4].

2007 wurde eine verbesserte Variante des Cell-Prozessors auf den Markt gebracht, der PowerXCell 8i. Dieser wurde bereits vom Start weg in 65 nm gefertigt und unterstützt im Vergleich zu seinem Vorgänger Berechnungen mit Gleitkommazahlen doppelter Genauigkeit nativ, das heißt ohne Hilfsfunktionen und damit wesentlich schneller.

Einsatz

Der Cell-Prozessor wurde mit speziellem Augenmerk auf breitbandige Berechnungsanwendungen entwickelt, vor allem Grafikberechnung und Videokodierung/-dekodierung. Die erste kommerzielle Verwendung fand das Design im September 2006 in IBM-Bladeservern mit acht SPEs.[5] Wirklich populär wurde der Prozessor aber durch seinen Einsatz in Sonys Spielkonsole Playstation 3, wo er mit 3,2 GHz Takt läuft, jedoch nur mit sieben SPEs (entspricht insgesamt ca. 180 GFlops bei einfach genauen Gleitkommazahlen). So können auch Cell-Chips mit nur sieben funktionierenden SPEs noch verbaut werden, wodurch die Kosten gesenkt werden können. Des Weiteren wird der Prozessor auch in Fernsehern mit erweiterten Videofunktionen eingesetzt[6], Cell-Derivate mit nur vier SPEs finden auch in speziellen Notebooks von Toshiba Verwendung.[7][8] Der Nachfolgeprozessor PowerXCell 8i wird seit März 2007 in Servern eingesetzt.[9][10]

Weitere Informationen

Vergleich der Linpackperformance zwischen Cell BE und anderen Prozessoren

Vergleich der Linpackperformance[1] Linpack

1k×1k (DP)Taktfrequenz Höchstleistung Durchschnittliche

LeistungEffizienz SPU 3,2 GHz 1,83 GFlops 1,45 GFlops 79,23 % 8 SPUs 3,2 GHz 14,63 GFlops 9,46 GFlops 64,66 % Pentium 4 3,2 GHz 6,40 GFlops 3,10 GFlops 48,44 % Pentium 4 + SSE3 3,6 GHz 14,40 GFlops 7,20 GFlops 50,00 % Itanium 1,6 GHz 6,40 GFlops 5,95 GFlops 92,97 % Die Werte beziehen sich auf doppelt genaue Gleitkommazahlen (64 Bits), für die der Cell-Prozessor nicht optimiert ist. Linpack-Berechnungen mit einfach genauen Gleitkommazahlen (32 Bits) erreichen über 73 GFLOPS auf einem Cell-Prozessor mit acht SPUs.

Zudem ist es auch interessant, den Cell-Prozessor mit anderen Multiprozessoren zu vergleichen:

Multi-Array Prozessoren[11] Hersteller Prozessor Anzahl der Kerne Anzahl

der SIMD-

EinheitenFMUL+FADD

Performance

in Flop/sTakt

in GHzSpitzenleistung

in GFlop/sBLAS/SGEMM

in GFlop/sVerlustleistung

in WattAusführung IBM Cell BE 8 4 2 3,2 204,8 201 80 Prozessor Nvidia 8800Ultra (G80) 128 1 2 1,512 387,1 1 >170 Karte Nvidia 8800GTX (G80) 128 1 2 1,350 345,6 1052 120–170 Karte Nvidia GT200b n/a n/a n/a 0,648 1060 n/a 180–240 Karte ATI HD2900 XT (R600) 320 5 2 0,742 474,9 1 150–200 Karte ATI 1900XTX (R580) 48 4 2 0,65 249,6 120 130–1703 Karte ATI RV770 n/a n/a n/a 0,750 1200 n/a 80–160 Karte ClearSpeed CSX600[12] 96 1 2 0,25 48 25 10 Prozessor -

unbekannt

-

unter DirectX 9

-

ctm

Siehe auch

- Nebenläufigkeit

- Parallelisierung

- Pipeline (Prozessor)

- Simultaneous Multithreading

- Multicore-Prozessor

- PowerPC

- TRIPS-Prozessor

- Terascale-Prozessor

- H. Peter Hofstee

Weblinks

- IBM: Cell Broadband Engine (englisch)

- Cell Architecture Explained, Details zur Cell Broadband Engine (englisch)

- IBM: Cell Broadband Engine resource center (englisch)

Referenzen

- ↑ a b IBM: Cell Broadband Engine Architecture and its first implementation - A performance view

- ↑ D. Pham, S. Asano, M. Bolliger, M. Day, H. Hofstee, C. Johns, J. Kahle, A. Kameyama, J. Keaty, Y. Masubuchi, M. Riley, D. Shippy, D. Stasiak, M. Suzuoki, M. Wang, J. Warnock, S. Weitzel, D. Wendel, T. Yamazakiund K. Yazawa: The design and implementation of a first-generation CELL processor; International Solid-State Circuits Conference, Seiten 184–185, Februar 2005

- ↑ Introducing the IBM/Sony/Toshiba Cell Processor -- Part II: The Cell Architecture, Artikel auf Arstechnica vom 8. Februar 2005

- ↑ IBM Produces Cell Processor Using New Fabrication Technology, Nachricht auf X-bit Labs vom 12. März 2007

- ↑ IBM stellt Blade-Server-Modul mit Cell-Prozessoren vor, Nachricht auf Heise.de vom 13. September 2006

- ↑ Toshiba Demonstrates Cell Microprocessor Simultaneously Decoding 48 MPEG-2 Streams, Nachricht auf Tech-On vom 25. April 2005

- ↑ Toshiba Qosmio G55 - erstes Notebook mit SpursEngine, Nachricht auf Golem vom 18. Juni 2008

- ↑ Toshiba Qosmio® G55-Q802 Laptop Computers Specs & Customer Reviews, Produktspezifikation zum Notebook mit SpursEngine-Prozessor, einem Cell-Derivat

- ↑ IBM announces PowerXCell 8i, QS22 blade server, Nachricht auf Beyond3D vom 13. Mai 2008

- ↑ IBM BladeCenter QS22, Produktspezifikation zum IBM-Bladeserver mit PowerXCell 8i

- ↑ Zelluläre Strukturen in c't, Seite 197 ff, Ausgabe 12/2007, Heise-Verlag

- ↑ Clearspeed CSX700, Produktspezifikation zum CSX700-Prozessor

-

Wikimedia Foundation.

.png)

.png)