- Static random-access memory

-

Static random-access memory (deutsch: statisches RAM, Abkürzung: SRAM) bezeichnet einen elektronischen Speichertyp. Sein Inhalt ist flüchtig (volatil; engl. volatile), das heißt, die gespeicherte Information geht bei Abschaltung der Betriebsspannung verloren. Im Gegensatz zu dynamischem Speicher (DRAM), welcher zur Vermeidung von Datenverlust ein periodisches Auffrischen (engl. refresh) benötigt, kann der Dateninhalt im statischen RAM bei Anliegen der Betriebsspannung beliebig lange gespeichert werden, wovon sich auch die Bezeichnung dieses Speichertyps ableitet.

Der SRAM ist nicht zu verwechseln mit SDRAM-Speicherzellen, einer taktsynchronen dynamischen Speicherzelle (DRAM), und damit einer vollkommen anderen Speichertechnik.

Inhaltsverzeichnis

Eigenschaften und Aufbau

6-Transistor-Zelle in CMOS-Technologie

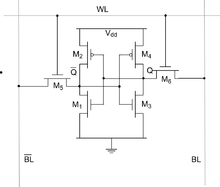

6-Transistor-Zelle in CMOS-Technologie

Die Informationen werden durch Zustandsänderung von einer bistabilen Kippstufe in Form eines Flipflops pro Bit gespeichert. Das erlaubt es zwar, die Speicherzelle schnell auszulesen, aber im Vergleich zu dynamischen Speicherzellen ist die Speicherzelle verhältnismäßig groß. Im statischen Betrieb (Halten der Information) ist der Leistungsbedarf einer Zelle sehr klein.

SRAMs werden heutzutage als 6-Transistor-Zelle in CMOS-Technologie hergestellt. Der Aufbau einer Kippstufe mit Widerständen als Lastelementen wird nicht mehr eingesetzt; statt der Lastwiderstände werden heute CMOS-Transistorpaare verwendet (siehe Bild). Mit weiteren zwei Transistoren zur Ankopplung an die Spalten- bzw. Zeilen-Auswahlleitungen ergibt sich die besagte 6-Transistor-Zelle wie im Bild anbei. Wegen dieses komplizierteren Aufbaus verbraucht eine SRAM-Zelle im Vergleich zu einer DRAM-Zelle deutlich mehr Chipfläche (über 140 F²).[1][2]

Schnittstellen

SRAMs werden mit unterschiedlichen Schnittstellen angeboten. Als diskretes Bauelement, primär für den direkten Anschluss an Mikrocontrollern, kommen parallele asynchrone Busschnittstellen zur Anwendung. Merkmal ist, dass der Zugriff auf den Speicher ohne Taktsignal erfolgt. Die Zugriffszeit pro Speicherzelle richtet sich nach der Laufzeit und liegt im Bereich von 5 ns bis zu knapp 100 ns. Darüber hinaus gibt es synchrone SRAMs bei welchen der Zugriff synchron zu einem Taktsignal erfolgt. Im Regelfall ist der Durchsatz von synchronen SRAMs höher als bei asynchronen SRAMs, da bei synchronen Schnittstellen die Möglichkeit besteht, mittels einer Pipeline die Adressen zu den Daten definiert zeitlich zu versetzen. Dies bringt vor allem bei sequentiellen Speicherzugriffen Geschwindigkeitsvorteile. Ein Beispiel von synchronen SRAMs sind die sogenannten „ZBT-SRAMs“ (engl. zero-bus-turnaround SRAM) welche bei schnellen Grafikspeichern Anwendung finden. [3] Für den Einsatz in Kombination mit DDR- und "Quad"-Speicher gibt es auch SRAMs, die entsprechend mehr Daten auf beiden Flanken des Taktsignals übertragen; hierbei werden Größen bis 72 MiBit (in der Organisation 4 Mi*18 oder 2 Mi*36) bei einer Taktfrequenz von 400 MHz erreicht.

Anwendungen

SRAMs finden als schneller Speicher mit vergleichsweise kleiner Datenkapazität überall dort Anwendung, wo der Dateninhalt schnell im Zugriff sein muss, wie beispielsweise in Prozessoren als Cache und auf digitalen oder Mixed-Signal-ICs wie FPGAs als lokaler Speicher auf dem Chip.

Weiterhin wird SRAM in Geräten eingesetzt, bei denen der Dateninhalt ohne dauerhafte Stromversorgung bis zu einigen Jahren gehalten werden soll. Da der Stromverbrauch im statischen Zustand (keine Speicherzugriffe) im Bereich einiger nA liegt, genügt eine kleine Pufferbatterie (u.U. auch ein Kondensator), um die nötige Versorgungsspannung bereitzustellen, beispielsweise beim CMOS-RAM zur Speicherung von BIOS-Einstellungen in handelsüblichen PCs. In diesem Anwendungsbereich stellt das SRAM in Kombination mit einer meist in Form einer Lithiumbatterie ausgeführten Pufferbatterie eine spezielle Form von NVRAM (engl. non-volatile random-access memory, nicht flüchtiger RAM) dar. Die Batterie kann in das Chipgehäuse des Speicherbausteins integriert sein.[4]

Einzelnachweise

- ↑ The International Technology Roadmap for Semiconductors 2007 - Emerging Research Devices, Seite 7 (engl., PDF)

- ↑ The International Technology Roadmap for Semiconductors 2007 - System Drivers (engl., PDF)

- ↑ Datenblatt eines synchronen ZBT-SRAMs (512 Ki × 36) (englisch)

- ↑ Datenblatt eines NV-SRAM. (DS2030 mit 32 Ki × 8 mit integrierter Pufferbatterie) (englisch)

Literatur

- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12 Auflage. Springer, Berlin 2002, ISBN 3-540-42849-6.

- Jörg Schulze: Konzepte siliziumbasierter MOS-Bauelemente. Springer, Berlin 2005, ISBN 3540234373.

Kategorien:- Speichermodul

- Hardware

- Halbleiterspeichertechnik

Wikimedia Foundation.