- Von-Neumann-Architektur

-

Die Von-Neumann-Architektur ist ein Referenzmodell für Computer, wonach ein gemeinsamer Speicher sowohl Computerprogrammbefehle als auch Daten hält. Von-Neumann-Systeme gehören nach der Flynnschen Klassifikation zur Klasse der SISD-Architekturen (Single Instruction, Single Data), im Unterschied zur Parallelverarbeitung.

Die Von-Neumann-Architektur bildet die Grundlage für die Arbeitsweise der meisten heute bekannten Computer. Sie ist benannt nach dem österreichisch-ungarischen, später in den USA tätigen Mathematiker John von Neumann, dessen wesentliche Arbeit zum Thema 1945 veröffentlicht wurde. Sie wird manchmal auch nach der gleichnamigen US-Universität Princeton-Architektur genannt.

Inhaltsverzeichnis

Entwicklung

Von Neumann beschrieb das Konzept 1945 in dem zunächst unveröffentlichten Papier „First Draft of a Report on the EDVAC“ im Rahmen des Baus der EDVAC-Rechenmaschine. Es war seinerzeit revolutionär, denn zuvor entwickelte Rechner waren an ein festes Programm gebunden, das entweder hardwaremäßig verschaltet war oder über Lochkarten eingelesen werden musste. Mit der Von-Neumann-Architektur war es nun möglich, Änderungen an Programmen sehr schnell und ohne Änderungen an der Hardware durchzuführen oder in kurzer Folge verschiedene Programme ablaufen zu lassen.

Viele Ideen der Von-Neumann-Architektur waren schon vorher 1936 von Konrad Zuse ausgearbeitet, in zwei Patentschriften 1937 dokumentiert und größtenteils bereits 1938 in der Z1-Maschine mechanisch realisiert worden. Es gilt aber als unwahrscheinlich, dass von Neumann die Arbeiten Zuses kannte, als er 1945 seine Architektur vorstellte.

Die meisten der heute gebräuchlichen Computer basieren auf dem Grundprinzip der Von-Neumann-Architektur, d.h. ihre Eigenschaften entsprechen einer VNA. Dies bedeutet jedoch typischerweise nicht mehr das sie intern wie eine einfache VNA mit den wenigen VNA-Funktionsgruppen aufgebaut sind. Im Laufe der Zeit wurden viele ursprünglich als einfache VNA-Rechnerarchitekturen erdachten, z.B. die x86-Architektur, jenseits davon ausdifferenziert und weitaus komplexer weiterentwickelt. Dies geschah um Leistungszuwächse zu erzielen, ohne jedoch mit dem leicht beherrschbaren VNA-Modell zu brechen, d.h. aus Softwaresicht kompatibel zu diesem bleiben um dessen Vorteile weiter nutzen zu können.

Mit dem Trend der wachsender Zahl der parallelen Recheneinheiten (Multicore) und Bussen (z.B. HyperTransport) wird diese Kompatibilität immer aufwändiger und schwieriger zu realisieren, es ist daher zu erwarten das sich in absehbarer Zukunft ein Paradigmenwechsel zu einem anderen, parallelen Architekturmodell notwendig sein wird um Leistungzuwächse in Rechnerarchitekuren erzielen zu können. Erste Vorboten sind zum Beispiel das aufkommende NUMA-Computing, bei dem der Speicher nicht mehr als mit "uniformen"-Eigenschaften behaftet betrachtet wird.

Konzept

Die Von-Neumann-Architektur ist ein Schaltungskonzept zur Realisierung universeller Rechner (Von-Neumann-Rechner, VNR). Sie realisiert alle Komponenten einer Turingmaschine. Dabei ermöglicht ihre systematische Aufteilung in die entsprechenden Funktionsgruppen jedoch die Nutzung spezialisierter binärer Schaltwerke und damit eine effizientere Strukturierung der Operationen.

Im Prinzip bleibt es aber dabei, dass alles, was mit einer Turingmaschine berechenbar ist, auch auf einer Maschine mit Von-Neumann-Architektur berechenbar ist und umgekehrt. Gleiches gilt für alle höheren Programmiersprachen, die durch einen Compiler oder Interpreter auf die binäre Repräsentation abgebildet werden. Sie vereinfachen zwar das Handling der Operationen, bieten jedoch keine Erweiterung der von der Turingmaschine vorgegebenen Semantik. Dies wird daran deutlich, dass die Übersetzung aus einer höheren Programmiersprache in die binäre Repräsentation wiederum von einem binären Programm ohne Anwenderinteraktion vorgenommen wird.

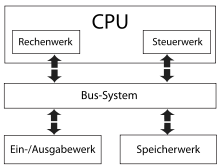

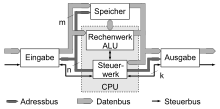

Komponenten

Ein Von-Neumann-Rechner beruht auf folgenden Komponenten, die bis heute in Computern verwendet werden:

- ALU (Arithmetic Logic Unit) – Rechenwerk, selten auch Zentraleinheit oder Prozessor genannt, führt Rechenoperationen und logische Verknüpfungen durch. (Die Begriffe Zentraleinheit und Prozessor werden i.Allg. in anderer Bedeutung verwendet.)

- Control Unit – Steuerwerk oder Leitwerk, interpretiert die Anweisungen eines Programms, und verschaltet dementsprechend Datenquelle, -senke und notwendige ALU-Komponenten; das Steuerwerk regelt auch die Befehlsabfolge.

- Memory – Speicherwerk speichert sowohl Programme als auch Daten, welche für das Rechenwerk zugänglich sind.

- I/O Unit – Eingabe-/Ausgabewerk steuert die Ein- und Ausgabe von Daten, zum Anwender (Tastatur, Bildschirm) oder zu anderen Systemen (Schnittstellen).

Programmablauf

Diese Komponenten arbeiten Programmbefehle nach folgenden Regeln ab.

- Prinzipien des gespeicherten Programms:

- Befehle sind in einem RAM-Speicher mit linearem (1-dimensionalem) Adressraum abgelegt.

- Ein Befehls-Adressregister, genannt Befehlszähler oder Programmzähler, zeigt auf den nächsten auszuführenden Befehl.

- Befehle können wie Daten geändert werden.

- Prinzipien der sequentiellen Programm-Ausführung (siehe auch Von-Neumann-Zyklus):

- Befehle werden aus einer Zelle des Speichers gelesen und dann ausgeführt.

- Normalerweise wird dann der Inhalt des Befehlszählers um Eins erhöht.

- Es gibt einen oder mehrere Sprung-Befehle, die den Inhalt des Befehlszählers um einen anderen Wert als +1 verändern.

- Es gibt einen oder mehrere Verzweigungs-Befehle, die in Abhängigkeit vom Wert eines Entscheidungs-Bit den Befehlszähler um Eins erhöhen oder einen Sprung-Befehl ausführen.

Eigenschaften

Vorteile

Der streng sequentielle Ablauf einer Von-Neumann-Architektur ist der entscheidende Vorteil gegenüber anderen, parallelen Architekturen (z.B. Cluster (Computer), Harvard-Architektur) und der Grund für die ungebrochene Popularität dieser Architektur. Aus der Sicht des Programmierers ist ein einfacher, deterministischer Programmablauf garantiert, Race-Conditions und Daten-Inkohärenzen sind durch den einzelnen Bus, über den die CPU auf Daten und Programm zugreift, ausgeschlossen.

Von-Neumann-Flaschenhals

Der Von-Neumann-Flaschenhals der Von-Neumann-Architektur bezeichnet den architektonischen Sachverhalt, dass das Verbindungssystem (Daten- und Befehls-Bus) zum Engpass zwischen dem Prozessor und dem Speicher wird. Weitergehend beschreibt der Von-Neumann-Flaschenhals auch das für diesen Sachverhalt verantwortlichen Konzepts des „immer nur eine Sache auf einmal„ (eng. Original: word-at-a-time thinking), also den expliziten, erzwungenen Sequentialismus durch den einzigen Bus über den alle Aktionen laufen.

Der Begriff selbst, „Von-Neumann-Flaschenhals“ (eng. von neumann bottleneck), wurde von John Backus geprägt, welcher ihn in seiner 1977 ACM Turing Award Rede einführte:

Surely there must be a less primitive way of making big changes in the store than by pushing vast numbers of words back and forth through the von Neumann bottleneck. Not only is this tube a literal bottleneck for the data traffic of a problem, but, more importantly, it is an intellectual bottleneck that has kept us tied to word-at-a-time thinking instead of encouraging us to think in terms of the larger conceptual units of the task at hand. Thus programming is basically planning and detailing the enormous traffic of words through the von Neumann bottleneck, and much of that traffic concerns not significant data itself, but where to find it.[1]

Memory Wall

Da bei einer Von-Neumann-Architektur im Gegensatz zur Harvard-Architektur nur ein gemeinsamer Bus für Daten und Befehle genutzt wird, müssen sich diese die maximal übertragbare Datenmenge aufteilen. Bei frühen Computern stellte die CPU die langsamste Einheit des Rechners dar, d. h., die Datenbereitstellungzeit war nur ein geringer Anteil an der gesamten Verarbeitungszeit für eine Rechenoperation. Seit geraumer Zeit jedoch wuchs die CPU-Verarbeitungsgeschwindigkeit deutlich stärker als die Datentransferraten der Busse oder der Speicher, was den Einfluss des Von-Neumann-Flaschenhals verschärft.

Der Begriff der „memory wall“ bezeichnet dieses wachsende Ungleichgewicht zwischen der Geschwindigkeit der CPU und des Speichers außerhalb des CPU-Chips. Von 1986 bis 2000, wuchsen die CPU-Geschwindigkeiten jährlich um 55% während die Speichertransfergeschwindigkeit nur um 10% anstiegen. Diesem Trend folgend wird erwartet, dass die Speicherlatenz der Flaschenhals der Computerrechenleistung werden wird.[2]

Aktuell hat sich jedoch auch das CPU-Leistungswachstum signifikant abgeschwächt, teilweise durch physikalische Grenzen und teilweise auch weil aktuelle CPU-Designs bereits auf die Memory-wall getroffen sind. Intel fasste diese Gründe folgendermaßen zusammen:

„First of all, as chip geometries shrink and clock frequencies rise, the transistor leakage current increases, leading to excess power consumption and heat... Secondly, the advantages of higher clock speeds are in part negated by memory latency, since memory access times have not been able to keep pace with increasing clock frequencies. Third, for certain applications, traditional serial architectures are becoming less efficient as processors get faster (due to the so-called Von Neumann bottleneck), further undercutting any gains that frequency increases might otherwise buy. In addition, partly due to limitations in the means of producing inductance within solid state devices, resistance-capacitance (RC) delays in signal transmission are growing as feature sizes shrink, imposing an additional bottleneck that frequency increases don't address.“[3]

Eine andere Analyse betrachtet vor allem den kapazitiven Widerstand als Hindernis[4] und sieht ein maximales jährliches Wachstum von 12,5% im Mittel der CPU-Leistungen zwischen 2000 and 2014 voraus.

Harvard-Architektur

Eine der wichtigsten Konkurrenzarchitekturen ist die Harvard-Architektur mit einer physikalischen Separierung von Befehls- und Datenspeicher, auf die über getrennte Busse zugegriffen wird, also unabhängig und parallel. Der Vorteil dieser Architektur besteht darin, dass Befehle und Daten gleichzeitig geladen, bzw. geschrieben werden können, also potentiell der Von-Neumann-Flaschenhals umgangen werden kann. Der potentielle Nachteil gegenüber der Von-Neumann-Architektur ist der aller paralleler Systeme, die möglichen Race Conditions bei den Daten- und Befehlszugriffen und ein damit nicht-deterministischer Programmablauf.

Zudem sorgt die physikalische Trennung von Daten und Programm dafür, dass einfach eine Zugriffsrechtetrennung und Speicherschutz realisierbar ist. Um z.B. zu verhindern, dass bei Softwarefehlern Programmcode überschrieben werden kann, wurde (vor allem historisch) für den Programmcode ein im Betrieb nur lesbarer Speicher (z.B. ROM, Lochkarten) verwendet, für die Daten schreib- und lesbarer Speicher (z.B. RAM, Ringkernspeicher). Einzelne Elemente der Harvard-Architektur fließen seit den 1980er Jahren verstärkt wieder in die üblichen Von-Neumann-Rechner ein, da eine klarere Trennung von Befehlen und Daten die Betriebssicherheit erfahrungsgemäß deutlich erhöht. Besonders die gefürchteten Pufferüberläufe, die für die meisten Sicherheitslücken in modernen Systemen verantwortlich sind, werden bei stärkerer Trennung von Befehlen und Daten besser beherrschbar.

Nachteilig ist allerdings, dass nicht benötigter Datenspeicher nicht als Programmspeicher genutzt werden kann, also eine erhöhte Speicherfragmentierung auftritt.

Weblinks

- John von Neumann: First Draft of a Report on the EDVAC. (PDF, engl.) 1945

- Erklärung des Von Neumann Rechners des Department Informatik der Uni Hamburg mit Java-Applet zur Simulation

- MOPS ist ein Modellrechner mit Von-Neumann-Architektur

- JOHNNY ist ein vereinfachter Modellrechner mit Von-Neumann-Architektur speziell für den Informatikunterricht

Einzelnachweise

- ↑ John Backus: E. W. Dijkstra Archive: A review of the 1977 Turing Award Lecture (englisch). Abgerufen am 11. Juli 2008.

- ↑ Wm. A. Wulf (1. Dezember 1994): Hitting the Memory Wall: Implications of the Obvious (englisch) (pdf). www.cs.virginia.edu. Abgerufen am 3. August 2011.

- ↑ Platform 2015 documentation (PDF)

- ↑ Vikas Akarwal: Clock Rate versus IPC: The End of the Road for Conventional Microarchitectures (englisch) (pdf). University of Texas. Abgerufen am 3. August 2011.

Kategorien:- Rechnerarchitektur

- Von-Neumann-Rechner

- Geschichte der Informatik

Wikimedia Foundation.